Advances in Deflection Routing based Network on Chips

Dissertation zur Erlangung des naturwissenschaftlichen Doktorgrades der Julius-Maximilians-Universität Würzburg

vorgelegt von

# Armin Runge

aus Frankfurt a. M.

Würzburg 2017

# Advances in Deflection Routing based Network on Chips

Dissertation zur Erlangung des naturwissenschaftlichen Doktorgrades der Julius-Maximilians-Universität Würzburg

vorgelegt von

# Armin Runge

aus Frankfurt a. M.

Würzburg 2017

Eingereicht am: 13.02.2017 bei der Fakultät für Mathematik und Informatik 1. Gutachter: Prof. Dr. Reiner Kolla 2. Gutachter: Prof. Dr. Martin Radetzki

## Abstract

The progress which has been made in semiconductor chip production in recent years enables a multitude of cores on a single die. However, due to further decreasing structure sizes, fault tolerance and energy consumption will represent key challenges. Furthermore, an efficient communication infrastructure is indispensable due to the high parallelism at those systems. The predominant communication system at such highly parallel systems is a Network on Chip (NoC). The focus of this thesis is on NoCs which are based on deflection routing. In this context, contributions are made to two domains, fault tolerance and dimensioning of the optimal link width. Both aspects are essential for the application of reliable, energy efficient, and deflection routing based NoCs.

It is expected that future semiconductor systems have to cope with high fault probabilities. The inherently given high connectivity of most NoC topologies can be exploited to tolerate the breakdown of links and other components. In this thesis, a fault-tolerant router architecture has been developed, which stands out for the deployed interconnection architecture and the method to overcome complex fault situations. The presented simulation results show, all data packets arrive at their destination, even at high fault probabilities. In contrast to routing table based architectures, the hardware costs of the herein presented architecture are lower and, in particular, independent of the number of components in the network.

Besides fault tolerance, hardware costs and energy efficiency are of great importance. The utilized link width has a decisive influence on these aspects. In particular, at deflection routing based NoCs, over- and under-sizing of the link width leads to unnecessary high hardware costs and bad performance, respectively. In the second part of this thesis, the optimal link width at deflection routing based NoCs is investigated. Additionally, a method to reduce the link width is introduced. Simulation and synthesis results show, the herein presented method allows a significant reduction of hardware costs at comparable performance.

## Kurzfassung

Die Fortschritte der letzten Jahre bei der Fertigung von Halbleiterchips ermöglichen eine Vielzahl an Rechenkernen auf einem einzelnen Chip. Die in diesem Zusammenhang immer weiter sinkenden Strukturgrößen führen jedoch dazu, dass Fehlertoleranz und Energieverbrauch zentrale Herausforderungen darstellen werden. Aufgrund der hohen Parallelität in solchen Systemen, ist außerdem eine leistungsfähige Kommunikationsinfrastruktur unabdingbar. Das in diesen hochgradig parallelen Systemen überwiegend eingesetzte System zur Datenübertragung ist ein Netzwerk auf einem Chip (engl. Network on Chip (NoC)). Der Fokus dieser Dissertation liegt auf NoCs, die auf dem Prinzip des sog. Deflection Routing basieren. In diesem Kontext wurden Beiträge zu zwei Bereichen geleistet, der Fehlertoleranz und der Dimensionierung der optimalen Breite von Verbindungen. Beide Aspekte sind für den Einsatz zuverlässiger, energieeffizienter, Deflection Routing basierter NoCs essentiell.

Es ist davon auszugehen, dass zukünftige Halbleiter-Systeme mit einer hohen Fehlerwahrscheinlichkeit zurecht kommen müssen. Die hohe Konnektivität, die in den meisten NoC Topologien inhärent gegeben ist, kann ausgenutzt werden, um den Ausfall von Verbindungen und anderen Komponenten zu tolerieren. Im Rahmen dieser Arbeit wurde vor diesem Hintergrund eine fehlertolerante Router-Architektur entwickelt, die sich durch das eingesetzte Verbindungsnetzwerk und das Verfahren zur Überwindung komplexer Fehlersituationen auszeichnet. Die präsentierten Simulations-Ergebnisse zeigen, dass selbst bei sehr hohen Fehlerwahrscheinlichkeiten alle Datenpakete ihr Ziel erreichen. Im Vergleich zu Router-Architekturen die auf Routing-Tabellen basieren, sind die Hardware-Kosten der hier vorgestellten Router-Architektur gering und insbesondere unabhängig von der Anzahl an Komponenten im Netzwerk, was den Einsatz in sehr großen Netzen ermöglicht.

Neben der Fehlertoleranz sind die Hardware-Kosten sowie die Energieeffizienz von NoCs von großer Bedeutung. Einen entscheidenden Einfluss auf diese Aspekte hat die verwendete Breite der Verbindungen des NoCs. Insbesondere bei Deflection Routing basierten NoCs führt eine Über- bzw. Unterdimensionierung der Breite der Verbindungen zu unnötig hohen Hardware-Kosten bzw. schlechter Performanz. Im zweiten Teil dieser Arbeit wird die optimale Breite der Verbindungen eines Deflection Routing basierten NoCs untersucht. Außerdem wird ein Verfahren zur Reduzierung der Breite dieser Verbindungen vorgestellt. Simulations- und Synthese-Ergebnisse zeigen, dass dieses Verfahren eine erhebliche Reduzierung der Hardware-Kosten bei ähnlicher Performanz ermöglicht.

## Danksagung

Mit der Abgabe dieser Dissertation endet ein bedeutender Abschnitt für mich und daher möchte ich mich bei einigen Menschen bedanken, die mich in den letzten Jahren unterstützt haben. Zu aller erst gilt mein besonderer Dank meinem Doktorvater Prof. Dr. Reiner Kolla, der mir schon in einer sehr frühen Phase meines Studiums die Möglichkeit gab als studentische Hilfskraft und später als wissenschaftlicher Mitarbeiter und Promotionsstudent im Team des Lehrstuhls für Technische Informatik zu arbeiten. Ebenfalls bedanken möchte ich mich bei Prof. Dr. Martin Radetzki für seine Anregungen und die Bereitschaft sich als Zweitgutachter für diese Dissertation zur Verfügung zu stellen.

Bedanken möchte ich mich außerdem bei allen aktuellen und ehemaligen Mitarbeiterinnen und Mitarbeitern des Lehrstuhls für Technische Informatik. Ich habe die tolle Arbeitsatmosphäre sowie die unzähligen Gespräche und fachlichen Diskussionen in der Elektronikwerkstatt, in der hin und wieder auch Kaffee gekocht wurde, sehr genossen. Insbesondere möchte ich mich bei Isabel Grimm und Johannes Mühr für das Lesen dieser Arbeit, sowie die hilfreichen Kommentare und Korrekturen bedanken.

Abschließend möchte ich mich noch bei meiner Familie und meinen Freunden bedanken. Ein besonderer Dank gilt meinen Eltern, die mir das Studium in Würzburg ermöglicht haben und dadurch den Grundstein für meine weitere wissenschaftliche Laufbahn gelegt haben. Ein ganz besonderer Dank gilt außerdem meiner Verlobten Isabel Grimm. Vielen Dank für deine Unterstützung und dein Verständnis in den letzten Monaten!

## Contents

| AŁ  | ostra                      | ct                                               | iii                  |

|-----|----------------------------|--------------------------------------------------|----------------------|

| Κι  | urzfas                     | ssung                                            | v                    |

| Da  | anksa                      | igung                                            | vii                  |

| Lis | st of                      | Tables                                           | xiii                 |

| Lis | st of                      | Figures                                          | xv                   |

| Ab  | brev                       | iations & Acronyms                               | xix                  |

| Sy  | mbo                        | ls                                               | xxi                  |

| 1   | <b>Intro</b><br>1.1<br>1.2 | Dduction<br>Motivation                           | <b>1</b><br>1<br>4   |

| 2   | Net                        | work Basics                                      | 7                    |

|     | 2.1                        | Building Blocks and Terminology                  | 8                    |

|     | 2.2                        | Topology                                         | 11                   |

|     | 2.3                        | Routing                                          | 14                   |

|     |                            | 2.3.1 Classification                             | 14                   |

|     |                            | 2.3.2 Routing Algorithms and Turn Model          | 15                   |

|     | 2.4                        | Buffering and Flow Control                       | 18                   |

|     |                            | 2.4.1 Bufferless Flow Control                    | 18                   |

|     |                            | <ul><li>2.4.2 Buffered Flow Control</li></ul>    | 19<br>24             |

|     | 2.5                        | 2.4.3 Buffer Availability                        | 24<br>24             |

|     | 2.6                        | Performance                                      | 2 <del>4</del><br>27 |

|     | 2.0                        | 2.6.1 Performance Metrics                        | 27                   |

|     |                            | 2.6.2   Evaluation Methodology                   | 29                   |

|     | 2.7                        | Conclusion and Existing Interconnection Networks | <u>3</u> 4           |

| 3   |                            | ection Routing based Router Architectures        | 37                   |

|     | 3.1                        | Principle of Deflection Routing                  | 37                   |

|   | 3.2 | Pros and Cons of Deflection Routing                               | 39  |

|---|-----|-------------------------------------------------------------------|-----|

|   | 3.3 | Deflection Routing Implementations                                | 42  |

|   |     | 3.3.1 Crossbar based Architectures                                | 43  |

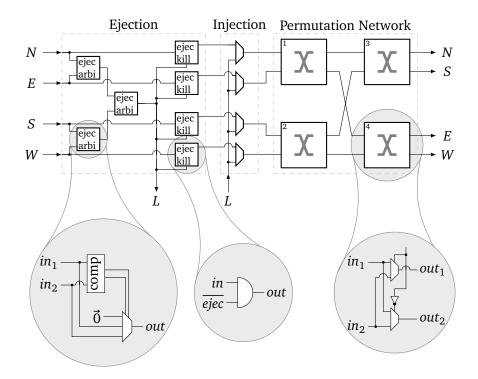

|   |     | 3.3.2 Permutation Network based Architectures                     | 46  |

|   | 3.4 | Basis Network on Chip and Router Architecture                     | 53  |

|   |     | -                                                                 | 54  |

|   |     | 3.4.2 Routing Algorithm                                           | 55  |

|   |     |                                                                   | 65  |

| 4 | Fau | It-tolerant and Deflection Routing based Router Architecture      | 67  |

|   | 4.1 | -                                                                 | 68  |

|   |     | -                                                                 | 69  |

|   |     |                                                                   | 71  |

|   |     | e e                                                               | 73  |

|   | 4.2 | Related Work of Chapter 4                                         | 73  |

|   | 4.3 | -                                                                 | 77  |

|   |     |                                                                   | 78  |

|   |     | •                                                                 | 86  |

|   |     | •                                                                 | 94  |

|   |     |                                                                   | 99  |

|   | 4.4 | Evaluation of FaFNoC Router Architecture                          | 100 |

|   |     | 4.4.1 Non-fault-tolerant Architecture                             | 101 |

|   |     | 4.4.2 Fault-tolerant Architecture                                 | 104 |

|   | 4.5 | Summary and Conclusion of Chapter 4                               | 111 |

| 5 | Des | ign of Deflection Routing based Network on Chips 1                | 13  |

|   | 5.1 |                                                                   | 13  |

|   |     |                                                                   | 114 |

|   |     | 5.1.2 Effect of the Link Width on Deflection Routing based NoCs 1 | 115 |

|   | 5.2 | Related Work                                                      | 117 |

|   | 5.3 | The optimal Link Width                                            | 119 |

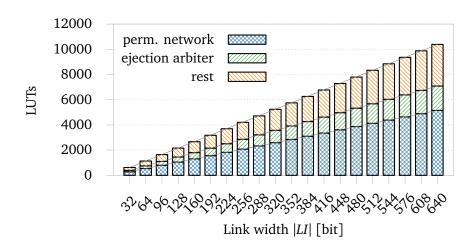

|   |     | 5.3.1 Effect of the Flit Size on Hardware Costs                   | 119 |

|   |     | 5.3.2 Effect of the Flit Size on Performance                      | 123 |

|   | 5.4 | TwoPhases - An Alternating Transmission Scheme                    | 132 |

|   |     | 5.4.1 Methodology of TwoPhases                                    | 133 |

|   |     | 5.4.2 Transmission Methods                                        | 139 |

|   |     | 5.4.3 Evaluation                                                  | 41  |

|   | 5.5 | Summary and Conclusion of Chapter 5                               | 149 |

| 6 | Con | ncluding Remarks                                                  | 151 |

|   |     | -                                                                 | 151 |

|    | 6.2                        | Future Work                            | 153 |

|----|----------------------------|----------------------------------------|-----|

| Α  | A.1                        | endix<br>Fault Situations of Chapter 4 |     |

| Pu | Publications of the Author |                                        |     |

| Bi | Bibliography               |                                        |     |

# List of Tables

| 2.1 | Metrics for different Network on Chip (NoC) topologies                   | 14  |

|-----|--------------------------------------------------------------------------|-----|

| 2.2 | Configuration of XST for synthesis.                                      | 29  |

| 2.3 | Bit permutation traffic patterns                                         | 30  |

| 2.4 | Characteristics of the three herein evaluated PARSEC benchmarks          | 32  |

| 2.5 | Characteristics of the interconnection architectures of real processors. | 35  |

| 4.1 | Several methods and techniques to enhance the reliability of NoCs        | 70  |

| 4.2 | Possible and impossible routing decisions of different interconnection   |     |

|     | architectures                                                            | 90  |

| 5.1 | Simulated link widths, and the consequential number of flits per large   |     |

|     | message as well as per small message                                     | 131 |

| 5.2 | PARSEC simulation results, for seven different link widths / flit sizes  | 131 |

| 5.3 | All Pareto optimal link withs for $ msg  = 32$ and $ hd  = 16. \dots$    | 142 |

| 5.4 | PARSEC simulation results, for three different clock ratios              | 146 |

# List of Figures

| 1.1  | Challenges of many-core processor design.                                              | 2  |

|------|----------------------------------------------------------------------------------------|----|

| 2.1  | Three communication infrastructures used in System-on-Chips                            | 9  |

| 2.2  | Data units at NoCs                                                                     | 10 |

| 2.3  | Flit structure of head, body, and tail flits                                           | 11 |

| 2.4  | Frequently used direct NoC topologies.                                                 | 12 |

| 2.5  | Routing dependent deadlock at a 2D mesh                                                | 16 |

| 2.6  | The turn model for a 2D mesh topology.                                                 | 17 |

| 2.7  | Classification of flow control mechanisms according to [DT04]                          | 18 |

| 2.8  | Time-space diagram of a transmission with store-and-forward flow control.              | 20 |

| 2.9  | Time-space diagram of a transmission with virtual cut-through flow control.            | 21 |

| 2.10 | Time-space diagram of a transmission with wormhole flow control                        | 22 |

| 2.11 | Time-space diagram of a transmission with virtual channel flow control.                | 23 |

| 2.12 | Block diagram of a typical input queued, virtual channel router, which                 |    |

|      | uses credit-based flow control, according to [MWM04]                                   | 25 |

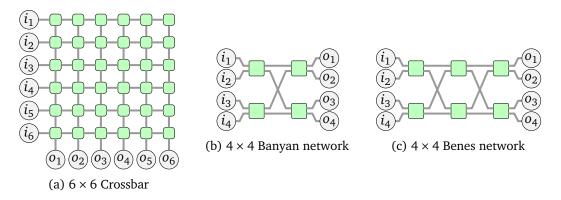

| 2.13 | Three indirect network topologies: $6 \times 6$ crossbar, $4 \times 4$ Banyan network, |    |

|      | and $4 \times 4$ Benes network                                                         | 26 |

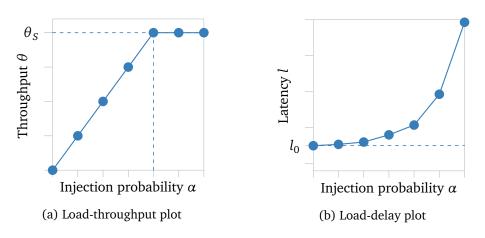

| 2.14 | Typical NoC performance metrics illustrated.                                           | 28 |

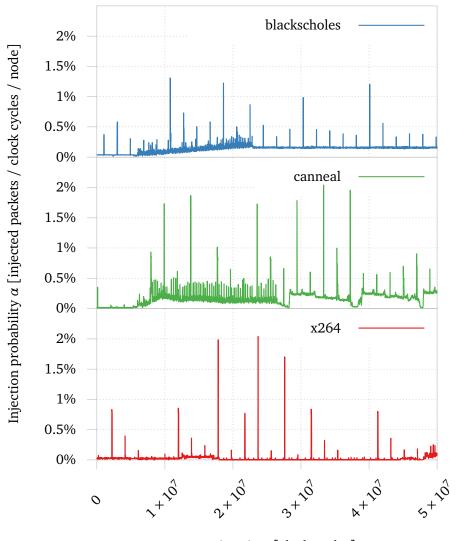

| 2.15 | Injection probabilities during the first 50 million clock cycles of the ROI            |    |

|      | of three PARSEC benchmarks.                                                            | 33 |

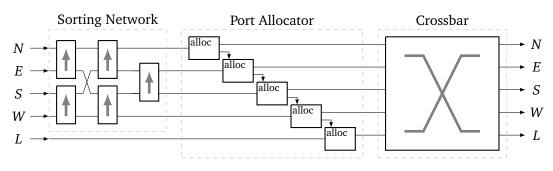

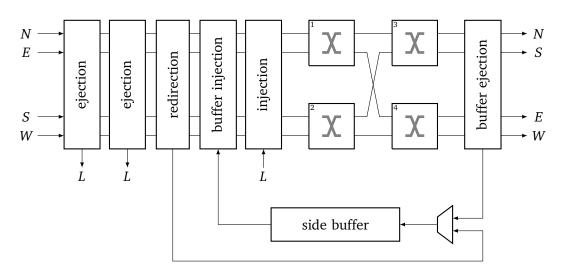

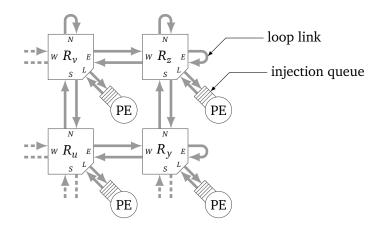

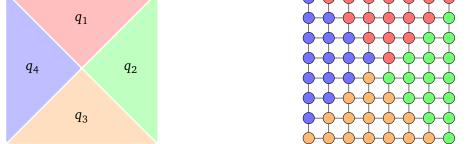

| 3.1  | Crossbar based router architecture                                                     | 43 |

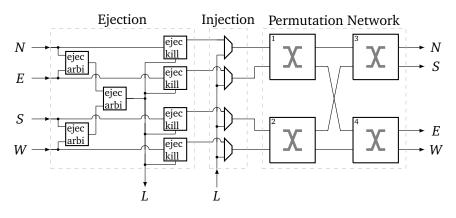

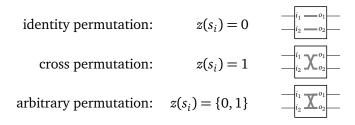

| 3.2  | CHIPPER router architecture [FCM10; FCM11]                                             | 47 |

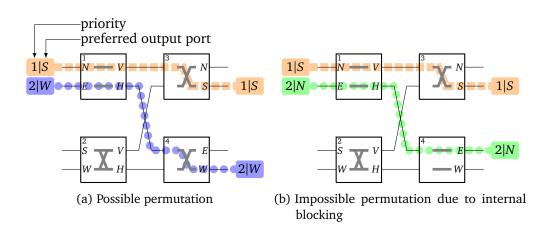

| 3.3  | A possible and an impossible permutation for a Banyan network                          | 49 |

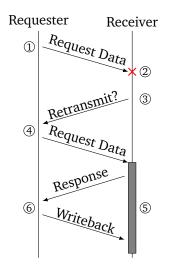

| 3.4  | Retransmit-once protocol scheme [FCM10, p. 12]                                         | 51 |

| 3.5  | MinBD router architecture [Fal+11; Fal+12]                                             | 52 |

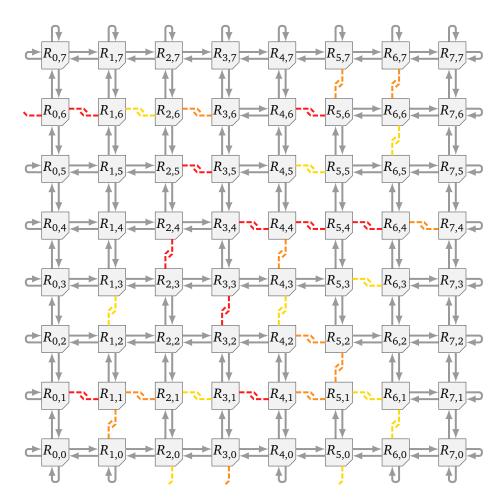

| 3.6  | 2D mesh topology with loop links at the edges of the mesh                              | 54 |

| 3.7  | At AVOID_CENTER, the used routing algorithm depends on the routers'                    |    |

|      | position                                                                               | 59 |

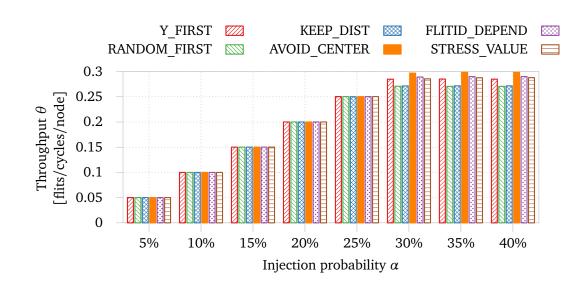

| 3.8  | Throughput for all evaluated routing algorithms and eight different in-                |    |

|      | jection probabilities.                                                                 | 62 |

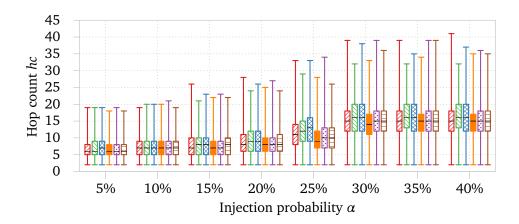

| 3.9  | Statistical values of the flits' hop count for all evaluated routing algorithms        |    |

|      | and eight different injection probabilities                                            | 62 |

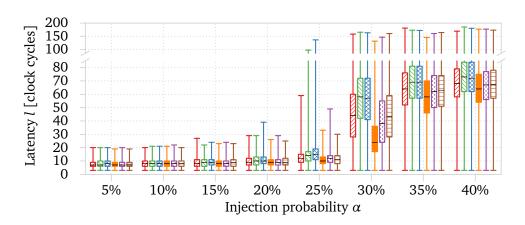

| 3.10  | Statistical values of the flits' latency for all evaluated routing algorithms         | 63         |

|-------|---------------------------------------------------------------------------------------|------------|

| 0 1 1 | and eight different injection probabilities.                                          |            |

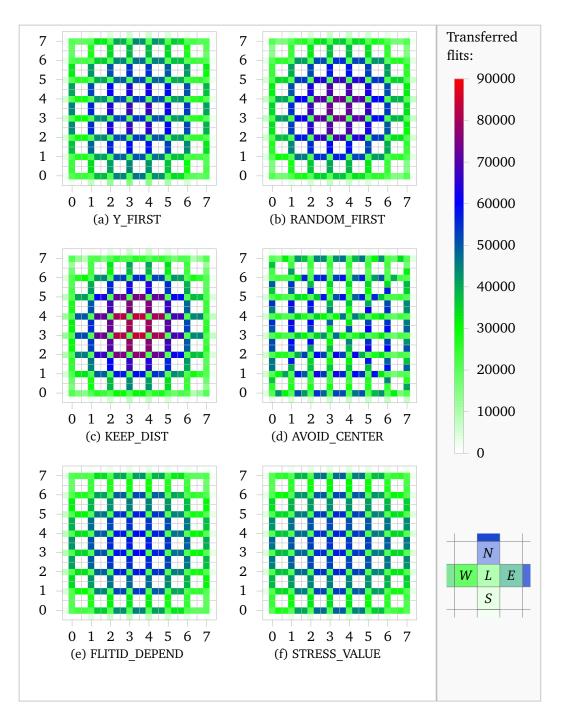

|       | Link utilization at an injection probability of $\alpha = 20\%$                       | 64         |

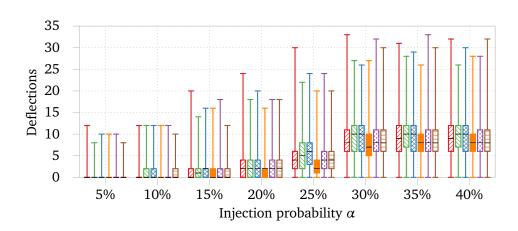

| 3.12  | Statistical values of the flits' deflections for all evaluated routing algo-          | <i>.</i> - |

|       | rithms and eight different injection probabilities                                    | 65         |

| 4.1   | Two fault shapes which are not tolerated by FoN.                                      | 75         |

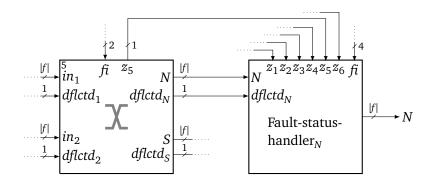

| 4.2   | Overview of the FaFNoC router architecture.                                           | 78         |

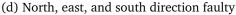

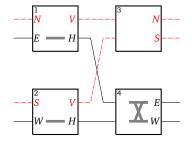

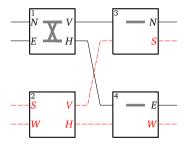

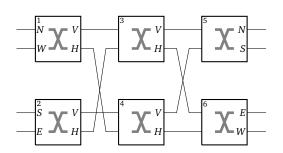

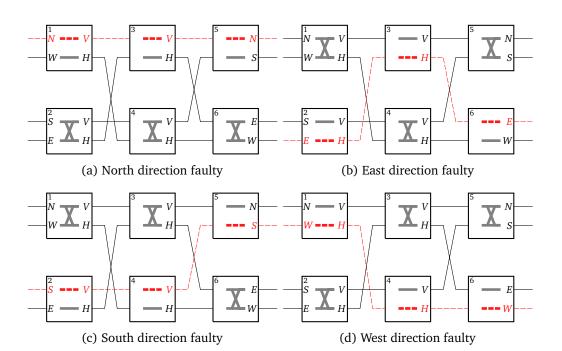

| 4.3   | All one-direction fault situations of a Banyan network.                               | 80         |

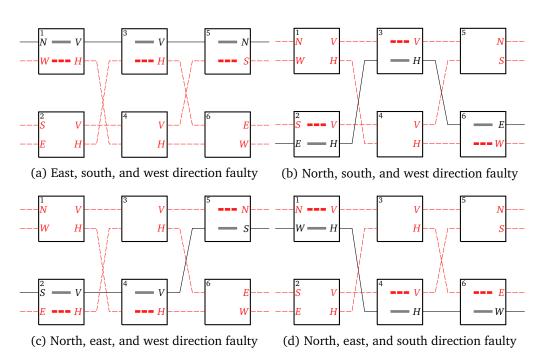

| 4.4   | All three-directions fault situations of a Banyan network                             | 81         |

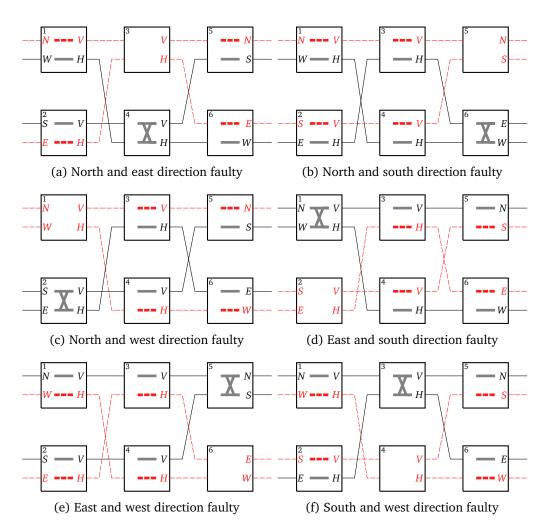

| 4.5   | All unambiguous two-directions fault situations of a Banyan network                   | 82         |

| 4.6   | All ambiguous two-directions fault situations of a Banyan network                     | 82         |

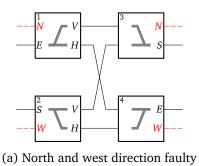

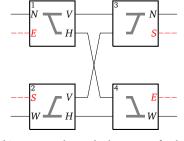

| 4.7   | Two fault situations, the first situation requires a reflection of flits,             |            |

|       | whereas reflections create a risk of livelocks at the second situation                | 84         |

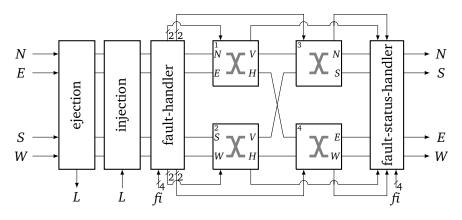

| 4.8   | Overview of the FaFNoC router architecture based on a Banyan network.                 | 85         |

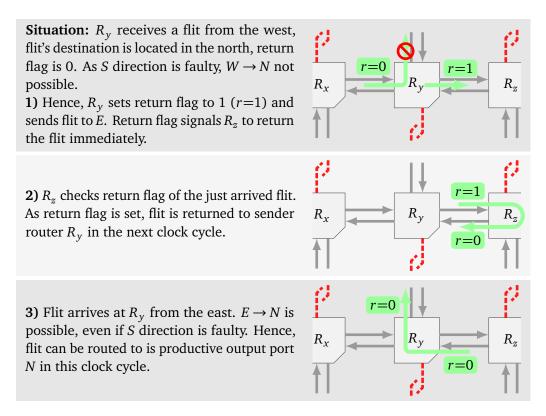

| 4.9   | Return flag handling of FaFNoC-Banyan illustrated.                                    | 87         |

| 4.10  | A 4×4 Benes network with configuration adopted from CHIPPER's Banyan                  |            |

|       | network.                                                                              | 88         |

| 4.11  | FaFNoC's Benes network, with a changed arrangement of input ports                     |            |

|       | as well as a changed wiring between the first and the second stage of                 |            |

|       | switching elements.                                                                   | 89         |

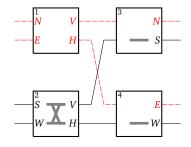

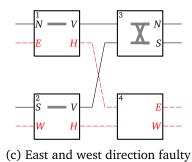

|       | All one-direction fault situations of a Benes network                                 | 92         |

| 4.13  | All two-directions fault situations of a Benes network.                               | 93         |

| 4.14  | All three-directions fault situations of a Benes network                              | 94         |

| 4.15  | Detailed illustration of switching element $s_5$ and fault-status-handler for         |            |

|       | north port                                                                            | 97         |

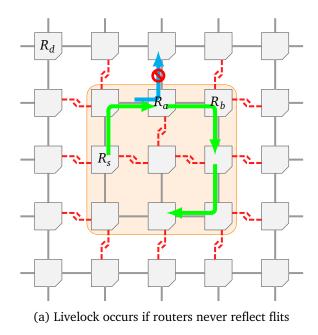

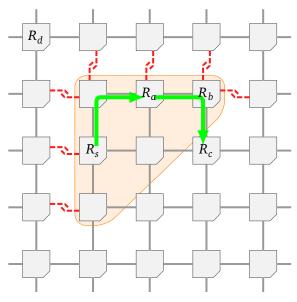

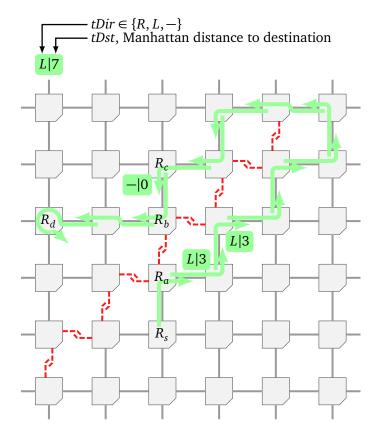

| 4.16  | Path of a flit which is routed from $R_s$ to $R_d$ . At $R_a$ , the flit is turned to |            |

|       | region evasion modus, and at $R_c$ , back to normal mode                              | 98         |

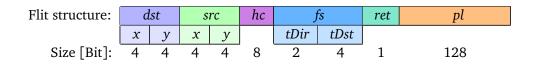

|       | FaFNoC's flit structure for an 8 × 8 NoC.                                             | 100        |

| 4.18  | Simulation results for non-fault-tolerant router architectures with differ-           |            |

|       | ent interconnection architectures, uniform random traffic, and a variable             |            |

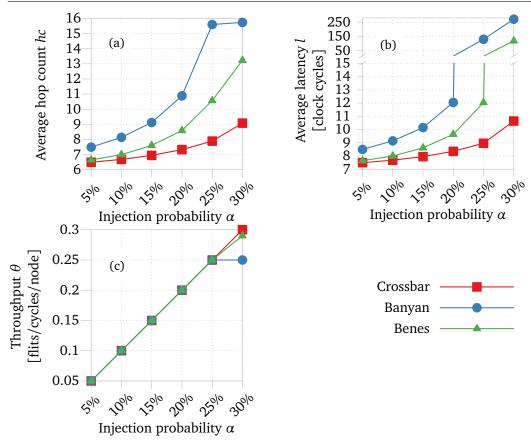

|       | injection probability.                                                                | 102        |

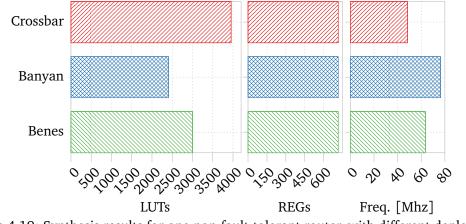

| 4.19  | Synthesis results for one non-fault-tolerant router, with different deployed          |            |

|       | interconnection architectures.                                                        | 102        |

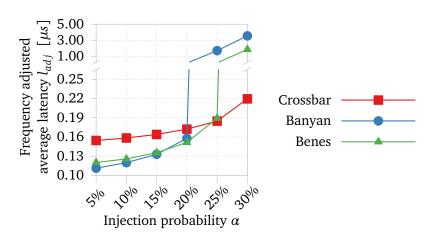

| 4.20  | Frequency adjusted average latency for non-fault-tolerant router archi-               |            |

|       | tectures.                                                                             | 103        |

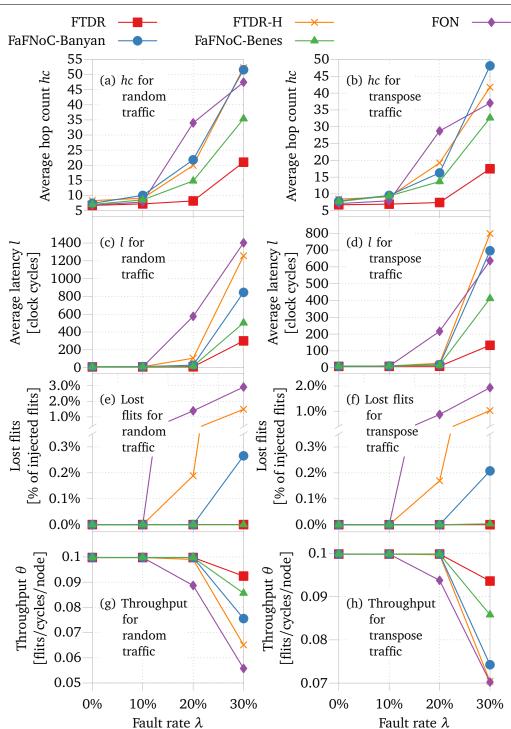

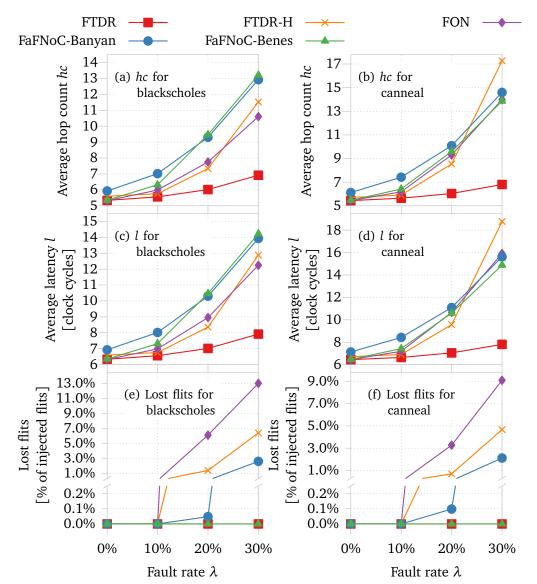

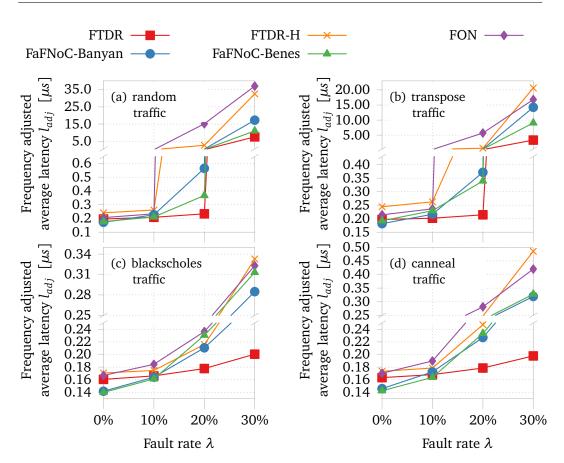

|       | Simulation results for random traffic and transpose traffic                           | 105        |

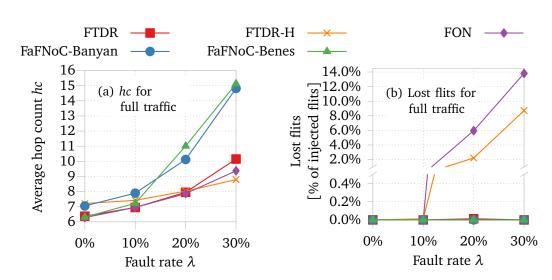

|       | Average hop count and percentage of lost flits for full traffic                       | 106        |

| 4.23  | Simulation results for two PARSEC benchmarks and a variable number                    |            |

|       | of random link failures.                                                              | 108        |

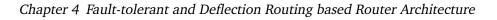

|            |                                                                                                 | 110          |

|------------|-------------------------------------------------------------------------------------------------|--------------|

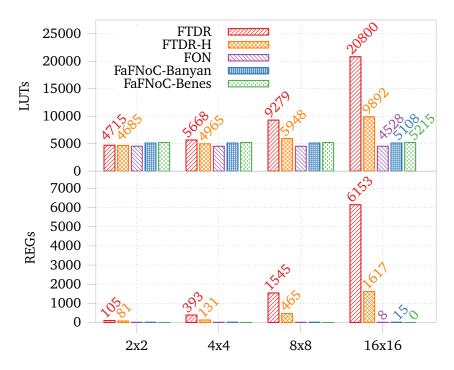

| 4.25       | Achievable frequencies for the herein compared fault-tolerant router architectures.             | 110          |

| 4.26       | Frequency adjusted average latency for fault-tolerant router architectures.                     |              |

| 5.1        | 1 0                                                                                             | 116          |

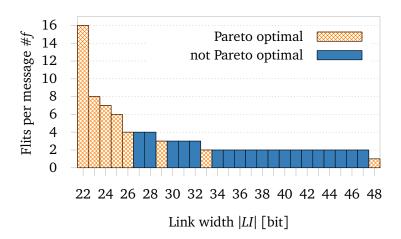

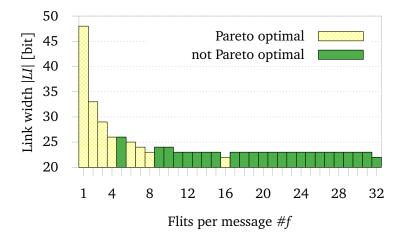

| 5.2        |                                                                                                 | 120          |

| 5.3        |                                                                                                 | 123          |

| 5.4        | 1 0                                                                                             | 125          |

| 5.5        | i C                                                                                             | 126          |

| 5.6<br>5.7 | Transmission of three flits between two two-hop neighbors                                       | 126          |

| 5.7        | e e                                                                                             | 128          |

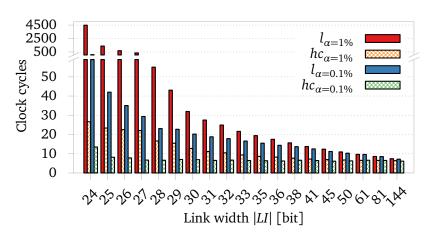

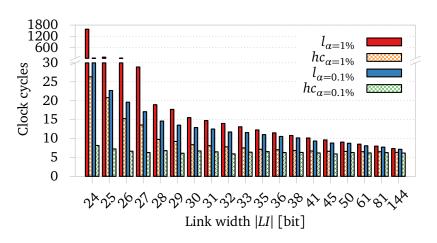

| 5.8        | Average latency <i>l</i> and average hop count <i>hc</i> for traffic with uniform length.       |              |

| 5.9        | Average latency $l$ and average hop count he for traffic with non-uniform                       |              |

|            |                                                                                                 | 130          |

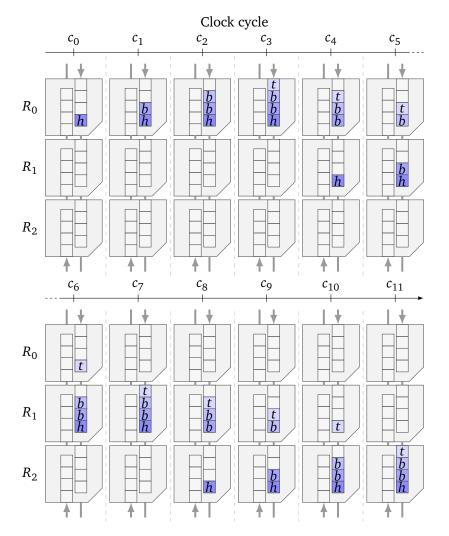

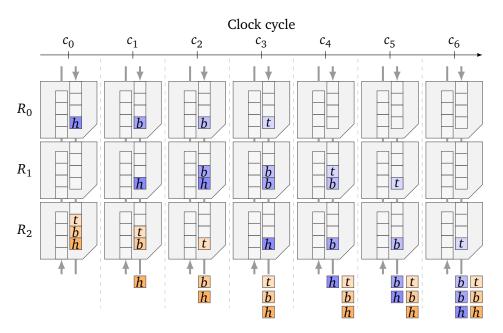

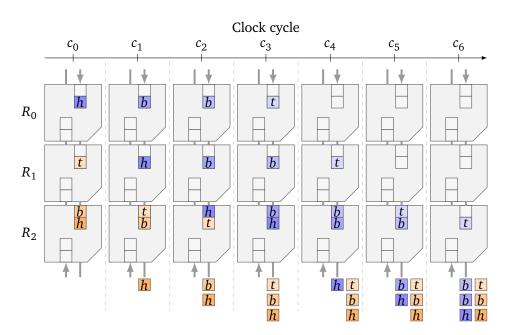

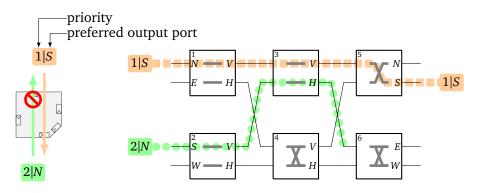

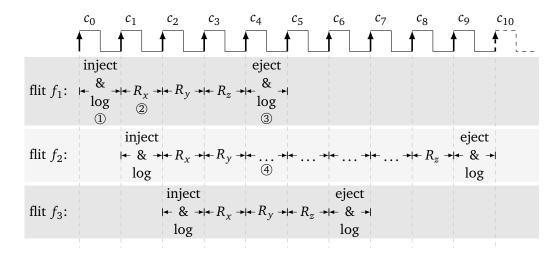

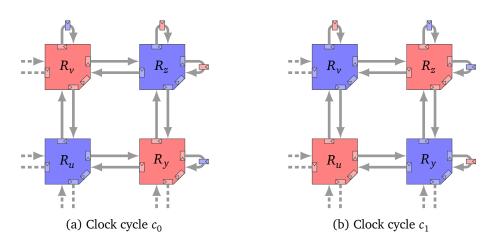

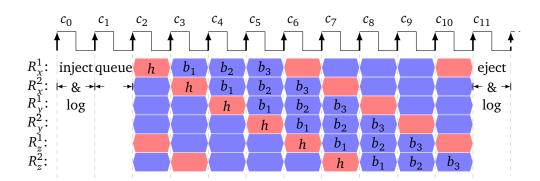

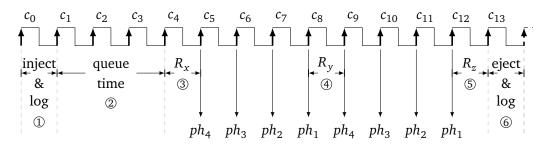

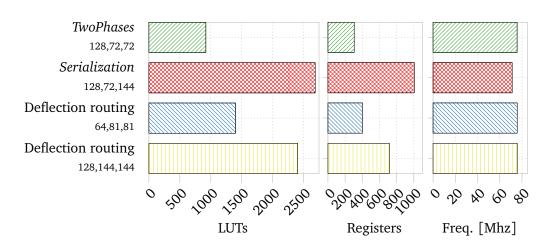

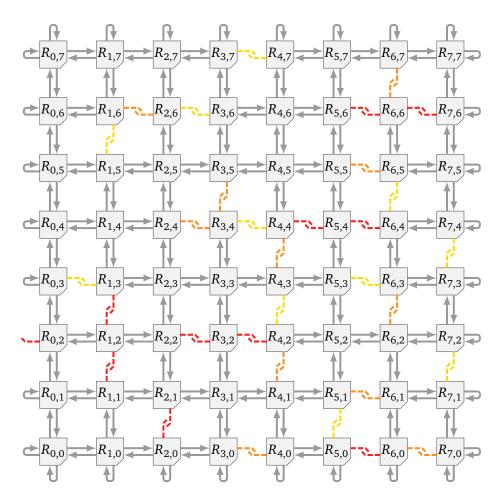

| 5.10       | Mesh topology with <i>TwoPhases</i> for two consecutive clock cycles                            | 134          |

| 5.11       | Transmission of one packet, which is routed with <i>TwoPhases</i> from $R_x$ to                 |              |

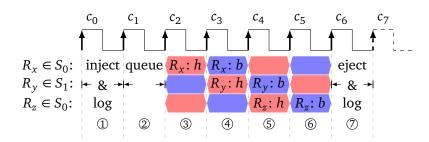

|            | 1 C 2 y                                                                                         | 136          |

| 5.12       | Transmission of one packet, which is routed with <i>TwoPhases</i> and a pipelined               |              |

|            | router architecture with two stages from $R_x$ to its two-hop neighbor $R_z$                    | 137          |

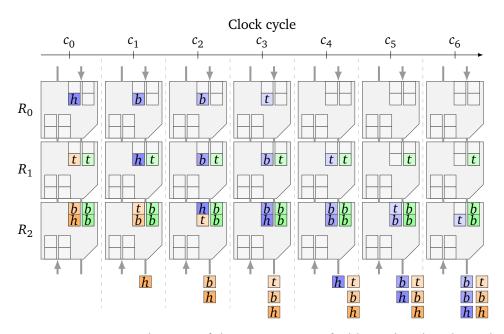

| 5 1 2      | via $R_y$<br>Transmission of one message with Serialization between two-hop neighbors.          |              |

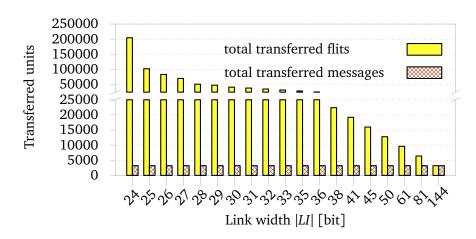

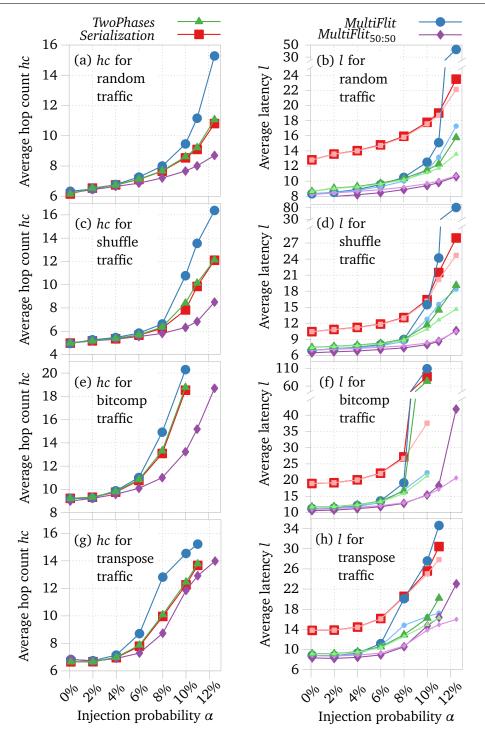

|            | Avgerage hop count <i>hc</i> and latency <i>l</i> for a variable injection probability $\alpha$ | 141          |

| 5.11       |                                                                                                 | 144          |

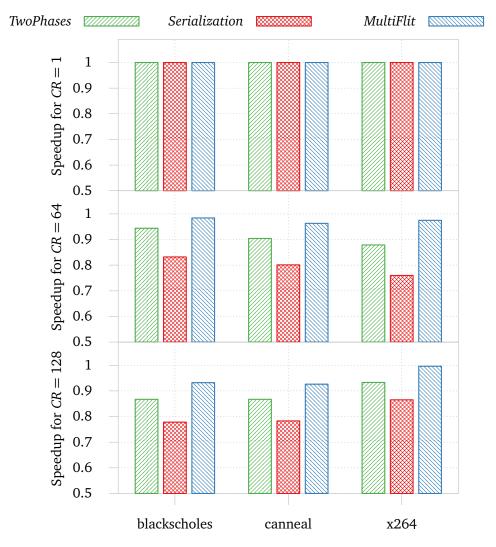

| 5.15       | Speedup for all evaluated PARSEC simulations, compared to standard                              |              |

|            |                                                                                                 | 147          |

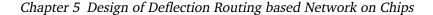

| 5.16       | Synthesis results for different router architectures                                            | 148          |

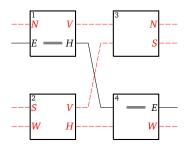

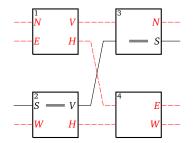

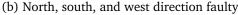

| A.1        | First simulated fault situation                                                                 | 156          |

| A.2        |                                                                                                 | $150 \\ 157$ |

| A.3        |                                                                                                 | 158          |

# Abbreviations & Acronyms

| ACK     | ACKnowledgement                                     |

|---------|-----------------------------------------------------|

| ARQ     | Automatic Repeat reQuest                            |

| ASIC    | Application-Specific Integrated Circuit             |

| AXI     | Advanced eXtensible Interface                       |

| BE      | Best Effort                                         |

| BLESS   | BufferLESS routing algorithms                       |

| CHIPPER | CHeap-Interconnect Partially PErmuting Router       |

| CLB     | Configurable Logic Block                            |

| CMOS    | Complementary Metal-Oxide-Semiconductor             |

| CMP     | Chip MultiProcessor                                 |

| CRC     | Cyclic Redundancy Check                             |

| FaF     | Fault-aware Flits                                   |

| FaFNoC  | Fault-aware Flits NoC                               |

| FEC     | Forward Error Correction                            |

| fifo    | first in - first out                                |

| flit    | flow control digit                                  |

| FPGA    | Field-Programmable Gate Array                       |

| GT      | Guaranteed Throughput                               |

| HWR     | HardWare Requirement                                |

| I/O     | Input/Output                                        |

| ID      | IDentifier                                          |

| ILP     | Instruction-Level Parallelism                       |

| IP      | Intellectual Property                               |

| ITRS    | International Technology Roadmap for Semiconductors |

| LUT     | LookUp Table                                        |

| MinBD   | Minimally-Buffered Deflection                       |

| MPSoC   | MultiProcessor System-on-Chip                       |

### Abbreviations & Acronyms

| MSHR        | Miss Status Holding Register                                     |

|-------------|------------------------------------------------------------------|

| <i>MUX</i>  | MUltipleXer                                                      |

| NACK        | Negative-ACKnowledgement                                         |

| NI          | Network Interface                                                |

| NoC         | Network on Chip                                                  |

| OCP         | Open Core Protocol                                               |

| PARSEC      | Princeton Application Repository for Shared-Memory Computers     |

| PE          | Processing Element                                               |

| phit        | physical transfer digit                                          |

| REG         | REGister                                                         |

| ROI         | Region Of Interest                                               |

| SEC code    | Single-Error Correcting code                                     |

| SECDED code | Single-Error Correcting and Double-Error Detecting code          |

| SEU         | Single Event Upset                                               |

| SoC         | System-on-Chip                                                   |

| TDM         | Time-Division Multiplexing                                       |

| TMR         | Triple Modular Redundancy                                        |

| TSV         | Through-Silicon Via                                              |

| VC          | Virtual Channel                                                  |

| VCI         | Virtual Component Interface                                      |

| VHDL        | Very high speed integrated circuit Hardware Description Language |

| VLSI        | Very-Large-Scale Integration                                     |

# Symbols

| $egin{array}{c} lpha \ \lambda \ 	heta \end{array}$                  | injection probability [flits/clock cycle/node]<br>fault rate, probability that a specific link is defect<br>throughput [flits/clock cycle/node]                                                                                                                                                                                                     |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b <sub>i</sub>                                                       | i-th body flit of a packet                                                                                                                                                                                                                                                                                                                          |

| c <sub>i</sub>                                                       | i-th network clock cycle                                                                                                                                                                                                                                                                                                                            |

| $d_1(\cdot)$<br>dst                                                  | Manhattan distance of $\cdot$ to destination [hops] destination address of a flit, field in the flit structure                                                                                                                                                                                                                                      |

| Ε                                                                    | port to the east                                                                                                                                                                                                                                                                                                                                    |

| $\begin{array}{l} fi \\ f_i \\ \#f \\ \ f\  \\ fs \\ ft \end{array}$ | fault information, routers' input vector with a width of <i>P</i> bit, <i>fi<sub>j</sub></i> gives the state of link <i>j</i> flit with ID i number of flits per message size of a flit [bit] fault status, field in the flit structure, which consists of <i>tDir</i> and <i>tDst</i> flit type, to distinguish between head, body, and tail flits |

| h<br>hc<br> hc <br>hd                                                | head flit of a packet<br>hop count of a flit, field in the flit structure<br>size of the <i>hc</i> field [bit]<br>header information of a flit, contains i.a.: flit's destination address,<br>flit's hop count<br>size of the header information [bit]                                                                                              |

| i <sub>i</sub><br>id<br> id                                          | i-th input<br>id of a flit, field in the flit structure<br>size of the <i>id</i> field [bit]                                                                                                                                                                                                                                                        |

| L<br>l                                                               | locale port<br>latency [clock cycle], time from when a flit enters the network to when<br>the flit departs the network                                                                                                                                                                                                                              |

| LI                                                                                | link width [bit]                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| msg <sub>i</sub><br> msg                                                          | message with ID i<br>size of a message <i>msg</i> [bit]                                                                                                                                                                                                            |

| Ν                                                                                 | port to the north                                                                                                                                                                                                                                                  |

| 0 <sub>i</sub>                                                                    | i-th output                                                                                                                                                                                                                                                        |

| P<br>P <sub>i</sub><br> p <br>ph <sub>i</sub><br>#ph<br> ph <br>pl<br> pl <br>pos | number of ports per router<br>packet with ID i<br>size of a packet [bit]<br>phit with ID i<br>number of phits per flit<br>size of a phit [bit]<br>payload of a flit, field in the flit structure<br>size of the <i>pl</i> field [bit]<br>address of current router |

| R <sub>i</sub>                                                                    | Router with ID i                                                                                                                                                                                                                                                   |

| S<br>s <sub>i</sub><br>src                                                        | port to the south<br>switching element / permute block with ID i<br>source address of a flit, field in the flit structure                                                                                                                                          |

| t<br>$t_{ejec}(\cdot)$<br>$t_{injec}(\cdot)$<br>tDir<br>tDst                      | tail flit of a packet<br>ejection time of $\cdot$<br>injection time of $\cdot$<br>turn direction, $tDir \in \{R, L, 0\}$ , field in the flit structure for fault toler-<br>ance<br>turn distance, field in the flit structure for fault tolerance                  |

| W                                                                                 | port to the west                                                                                                                                                                                                                                                   |

| $z(\cdot)$                                                                        | state of switching element $\cdot, z \in \{0, 1\}$                                                                                                                                                                                                                 |

# Chapter **1**

## Introduction

### Contents

| 1.1 | Motivation                                  | 1 |

|-----|---------------------------------------------|---|

| 1.2 | Thesis Outline and Scientific Contributions | 4 |

### 1.1 Motivation

Technology scaling has been following the self-fulfilling Moore's law [Moo98] for several generations of semiconductor chips. According to Gordon Moore's prediction, the number of transistors per unit area on integrated circuits doubled every two years. However, an end of traditional transistor scaling was predicted in the latest International Technology Roadmap for Semiconductors (ITRS) report [ITR15] for the 2020s, and also Gordon Moore expects an end of his own prediction, as technology scaling gets close to the atomic limitation [Cou15]. Nevertheless, chips with billions of transistors are already commercially available [Saw+11]. Recently, Gordon Moore stated in an interview:

"But we will be able to make several billion transistors on an integrated circuit at that time. And the room this allows for creativity is phenomenal." [Cou15]

In addition to great opportunities, technology scaling implicates several challenges. For several decades, Dennard scaling [Den+74], which essentially suggests that power requirements of a transistor are proportional to its area, has allowed manufactures to raise clock frequencies without significantly increasing overall circuit power consumption. Since around 2005-2007, Dennard scaling no longer seems to apply. Current leakage poses major challenges and a heat up of the chips, which further increases energy consumption. This leads to an inability to increase clock frequencies significantly and created a so called *power wall*.

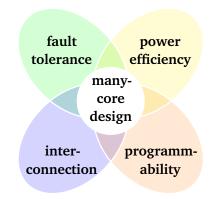

Figure 1.1: Challenges of many-core processor design.

Until recently, the utilization of Instruction-Level Parallelism (ILP) techniques was another key factor to improve processor performance. However, it became increasingly difficult to find enough parallelism in a single instruction stream to utilize the capacity of high-performance single-core processors. This lack of available instruction-level parallelism is called the *ILP wall*. Therefore, chip manufactures have focused on techniques to exploit higher levels of parallelism, as multithreading, and finally multi- and many-core processors.

The trend towards many-core processors is also confirmed by Pollack's Rule [Bor07]. This rule states that performance increase is roughly proportional to the square root of the increase in complexity, i.e. area. In contrast, the power consumption increase is roughly linearly proportional to the increase in complexity. Consequently, this leads to chips with hundreds or thousands of low-complexity cores, as those chips can provide more performance than a single complex core<sup>1</sup>. Indeed, chips with hundreds of cores on a single die exist and are commercially available nowadays. These chips range from Chip MultiProcessors (CMPs), which are usually homogeneous, and frequently tile-based, to heavily customized MultiProcessor System-on-Chips (MPSoCs), which are usually very heterogeneous.

The design of many-core processors also entails several challenges, as programmability, power efficiency, fault tolerance and interconnection (cf. Figure 1.1). Parallel programming paradigms are required to be able to utilize the processing power provided by these systems. Moreover, technology scaling and shrinking manufacturing processes have several undesirable side-effects, like an increasing variability in performance and reliability as well as a significant energy consumption [Bor05]. The increasing number of transistors per chip leads to a power challenge. It is projected that the amount of

<sup>&</sup>lt;sup>1</sup>Obviously, the workload has to contain enough parallelism to utilize the performance of all available cores.

dark silicon, i.e. the part of a chip which has to be powered-off to comply with power constraints, may reach up to 50% - 80% at 8 nm technology [Esm+11]. In addition, those systems have to cope with highly varying component lifetimes. Hence, fault tolerance concepts will be required to achieve reasonable operating periods and to improve yield rate. Furthermore, the increasing number of components on a single die leads to growing communication requirements. Traditionally deployed communication infrastructures, like buses, rings, and crossbars, can not provide the required high bandwidth, low latency, and energy efficiency, as they do not scale with the high number of communication participants.

For some of the above mentioned challenges solutions have yet to be found, but Network on Chips (NoCs) provide a scalable, parallel communication infrastructure. Thus, they are considered as the dominant interconnection architecture of many-core processors. They are also complex systems, with a multitude of design parameters. Indeed, today's NoCs consume a significant proportion of die area and system power [Bor07; Bor10]. The NoC of Intel's 80-Core Teraflops Research Chip, for example, consumes 17% of die area [Van+08] and 28% of system power [Hos+07]. Most utilized NoCs are buffered, packet switched networks and a very large part of the area and the energy is consumed by the networks' buffers. For instance, 60% die area of the iMesh NoC of Tilera's TILE64 many-core system is dedicated to buffering [Wen+07] and for the TRIPS chip, it is reported that the router's input buffers even occupy 75% of the router area [Gra+06]. At Intel's Teraflops Research Chip, buffer queues consume 22% of the communication power [Van+08]. Consequently, avoiding these buffers can contribute to reduce the power requirements of NoCs. The main focus of this thesis in on bufferless deflection routing, which has already been proposed in 1964 by Baran [Bar64]. At deflection routing, the data units of an NoC are not buffered by routers of the network, i.e. they can not wait at a router for resource allocation. Instead, if two data units try to allocate the same path, one data unit is routed along a potentially non-shortest path, i.e. it is deflected. Comparisons to buffered, packet switched NoCs demonstrated that bufferless, deflection routing based networks require over 30% less power and area [FCM10; CMM15].

Besides power efficiency, fault tolerance is an important aspect of many-core systems and, as such, also of NoCs. Generally, fault tolerance is achieved by adding some kind of redundancy. Most NoC topologies possess an inherent path redundancy. Thus, it suggests itself to exploit this redundancy to tolerate failures at the NoC level.

To summarize, power efficient, fault-tolerant NoCs are an important research topic and key components of future many-core systems. To quote Avinash Sodani, former Senior Principal Engineer at Intel and Chief Architect of Intel's Knights Landing Xeon-Phi processor:

"The developers of the ENIAC, [the earliest electronic general-purpose computer,] were faced with two challenges, and we are faced with the same

challenges today: reliability and interconnection." [Sod16]

This thesis contributes to the development of reliable and power efficient NoCs by:

- 1. presenting a fault-tolerant NoC based on a permutation network and additionally on deflection routing. Moreover, a new concept to overcome complex fault situations is introduced.

- investigating the effect of the link width on permutation network based router architectures. In addition, a new concept to reduce the routing overhead of a specific link width is presented.

### 1.2 Thesis Outline and Scientific Contributions

This thesis focuses on NoCs which utilize deflection routing and a permutation network based router architecture. An overview of NoCs, including main building blocks and terminology used in this context, is given in Chapter 2. The general principle of bufferless deflection routing is introduced in Chapter 3. Moreover, several existing implementations of deflection routing based NoCs and the basis router architecture used in this thesis are presented in Section 3.3 and Section 3.4, respectively. The main scientific contributions presented in this thesis are divided into two chapters.

Chapter 4 focuses on fault-tolerant and deflection routing based router architectures. This chapter starts with a brief introduction to fault tolerance at NoCs in Section 4.1. Existing fault-tolerant router architectures are presented in Section 4.2. Following this introduction, the FaFNoC router architecture, which has been developed as part of this thesis, is presented in Section 4.3. This architecture stands out for the utilized interconnection architecture and the method to tolerate complex fault situations. Most router architectures use either a crossbar or a  $4 \times 4$  Banyan network as interconnection architecture. Instead, a 4×4 Benes network is utilized at the FaFNoC architecture, which requires fewer hardware resources than a crossbar and provides significant benefits in terms of fault tolerance compared to a Banyan network. Moreover, every fault-tolerant router architecture requires some kind of global fault information to be able to overcome complex fault situations, as they can arise if several components fail. Existing approaches are based either on costly routing-tables or fault information of adjacent nodes. These approaches suffer from poor scalability or limited fault tolerance. Thus, the concept of Fault-aware Flits (FaF) has been developed, at which the transferred data units are aware of their encountered fault situation.

Chapter 5 addresses the design of deflection routing based NoCs, and specifically, the utilized link width. As an introduction and motivation, the effect of the link width on buffered, packet switched NoCs and bufferless, deflection routing based NoCs is compared in Section 5.1. The optimal link width and its effect on performance and

hardware requirements is considered in Section 5.3. Subsequently, *TwoPhases*, an alternating transmission scheme for deflection routing is presented in Section 5.4. Compared to standard deflection routing, *TwoPhases* allows a reduction of the routing overhead by more than half.

Both chapters close with a brief summary and conclusion. Finally, concluding remarks and an outlook to future work are provided in Chapter 6.

This thesis is based on the following publications:

- [Run12a] Armin Runge. Determination of the Optimum Degree of Redundancy for Fault-prone Many-Core Systems. In: Zuverlässigkeit und Entwurf - 6. GMM/GI/ITG-Fachtagung. VDE VERLAG GmbH, 2012

- [Run12b] Armin Runge. Reliability Enhancement of Fault-prone Many-core Systems Combining Spatial and Temporal Redundancy. In: 2012 IEEE 14th International Conference on High Performance Computing and Communication & 2012 IEEE 9th International Conference on Embedded Software and Systems. Institute of Electrical & Electronics Engineers (IEEE), June 2012. DOI: 10.1109/hpcc.2012.233

- [Run15a] Armin Runge. FaFNoC: A Fault-tolerant and Bufferless Network-onchip. In: Procedia Computer Science 56 (2015), pp. 397–402. DOI: 10. 1016/j.procs.2015.07.226

- [Run15b] Armin Runge. Fault-tolerant Network-on-Chip based on Fault-aware Flits and Deflection Routing. In: Proceedings of the 9th International Symposium on Networks-on-Chip. ACM. Association for Computing Machinery (ACM), 2015, p. 9. DOI: 10.1145/2786572.2786585

- [RK16a] Armin Runge and Reiner Kolla. An Alternating Transmission Scheme for Deflection Routing Based Network-on-Chips. In: Architecture of Computing Systems – ARCS 2016. Springer International Publishing. Springer Nature, 2016, pp. 48–59. DOI: 10.1007/978-3-319-30695-7\_4

- [RK16b] Armin Runge and Reiner Kolla. Consideration of the Flit Size for Deflection Routing based Network-on-Chips. In: 1st International Workshop on Advanced Interconnect Solutions and Technologies for Emerging Computing Systems (AISTECS). Association for Computing Machinery (ACM), 2016, 5:1–5:6. DOI: 10.1145/2857058.2857060

- [RK16c] Armin Runge and Reiner Kolla. TwoPhases: A Transmission Scheme to Reduce the Link Width at Deflection Routing based Network-on-Chips. In: Journal of Systems Architecture (Dec. 2016). DOI: 10.1016/j.sysarc. 2016.12.001

[RK16d] Armin Runge and Reiner Kolla. Using Benes Networks at Fault Tolerant and Deflection Routing based NoCs. In: *Proceedings of the 10th International Symposium on Networks-on-Chip*. Institute of Electrical and Electronics Engineers (IEEE), Sept. 2016. DOI: 10.1109/NOCS.2016.7579325

# Chapter 2

## **Network Basics**

### Contents

| 2.1 | Buildi                     | ng Blocks and Terminology 8                 |  |  |  |  |  |

|-----|----------------------------|---------------------------------------------|--|--|--|--|--|

| 2.2 | Topology                   |                                             |  |  |  |  |  |

| 2.3 | Routing                    |                                             |  |  |  |  |  |

|     | 2.3.1                      | Classification                              |  |  |  |  |  |

|     | 2.3.2                      | Routing Algorithms and Turn Model           |  |  |  |  |  |

| 2.4 | Buffering and Flow Control |                                             |  |  |  |  |  |

|     | 2.4.1                      | Bufferless Flow Control                     |  |  |  |  |  |

|     | 2.4.2                      | Buffered Flow Control                       |  |  |  |  |  |

|     | 2.4.3                      | Buffer Availability                         |  |  |  |  |  |

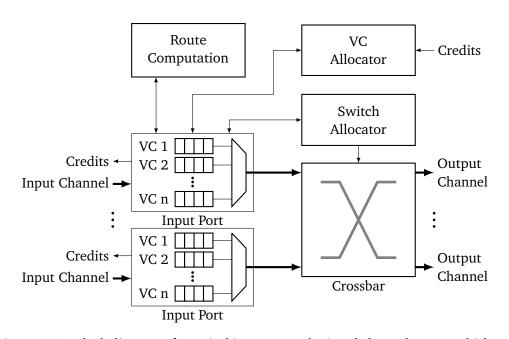

| 2.5 | Route                      | r Architecture                              |  |  |  |  |  |

| 2.6 | Performance                |                                             |  |  |  |  |  |

|     | 2.6.1                      | Performance Metrics                         |  |  |  |  |  |

|     | 2.6.2                      | Evaluation Methodology 29                   |  |  |  |  |  |

| 2.7 | Conclu                     | usion and Existing Interconnection Networks |  |  |  |  |  |

This chapter aims to give an overview of NoCs and introduce typical evaluation criteria in this field. Towards this end, the main building blocks, as well as the terminology used in this context, are introduced in Section 2.1. Subsequently, three important aspects of NoCs are presented in more detail, namely topology in Section 2.2, routing in Section 2.3, and flow control in Section 2.4. An overview of a typical virtual channel router architecture is provided in Section 2.5. Network performance metrics and the herein used evaluation methodologies are presented in Section 2.6. Finally, this chapter closes with a conclusion in Section 2.7, which includes an overview of several interconnection networks of existing processors.

### 2.1 Building Blocks and Terminology

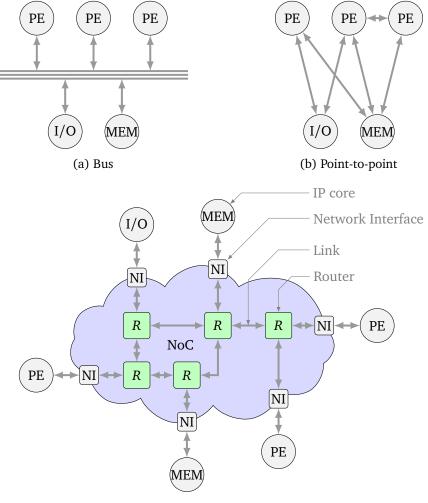

In general, NoCs provide a communication infrastructure for large systems, which consist of a huge number of communication participants or components. For such a high number of components, traditionally deployed communication infrastructures, e.g. buses and dedicated point-to-point links, do not scale or can not provide the required area, power, and timing requirements. An illustration of buses, point-to-point links, as well as an overview of NoCs, is depicted in Figure 2.1. This figure also shows the main building blocks of NoCs, namely *network interfaces* (NI), *routers* (*R*), and *links*.

Network interfaces<sup>2</sup> connect Intellectual Property (IP) cores, as processors, memories, or caches, to the network. They implement the conversion of messages, which are generated and processed by the IP cores, into packets, which can be routed by the network. Thus, network interfaces decouple computation from communication. A network interface consists of a front end and a back end. The front end is unaware of the NoC and usually adheres to a System-on-Chip (SoC) socket standard [BM06, p. 12], which is supported by the connected IP core. Sockets which already have been implemented in network interfaces include the Open Core Protocol (OCP) [Acc16], the Advanced eXtensible Interface (AXI) [ARM16], and the Virtual Component Interface (VCI) of the dissolved Virtual Socket Interface Alliance. The back end handles the network protocol, which involves, among others, end-to-end flow control handling as well as assembling and disassembling of packets.

The components of a network are connected by point-to-point links, which are composed of a set of wires. Depending on the definition, a link provides either a full-duplex or a simplex connection between the two components it connects. In this thesis, it is assumed that every link provides a simplex connection. However, components are connected by pairs of links. Thus, two links together enable a full-duplex communication between the two connected components.

One link can consist of several virtual or physical channels, which allows a parallel communication over this single link. Herein, every link consists of exactly one physical channel and potentially several virtual channels. More information about virtual channels is given in Section 2.4.2.

At most NoC topologies, the number of wires per link, also referred to as link width, is uniform throughout the NoC. However, network topologies with non-uniform link widths exist as well, e.g. the fat tree topology. Compared to off-chip networks, wires are cheap but the packet latency is critical. Therefore, links of NoCs are usually much wider than links of off-chip networks. Typical link widths of NoCs range from 16 bit to 512 bit.

The core elements of a NoC are routers. They consist of buffers, arbiters, and several Input/Output (I/O) ports. Routers receive packets from their input ports and forward them to their output ports. They implement a routing algorithm (cf. Section 2.3), as well

<sup>&</sup>lt;sup>2</sup>Network interfaces are also referred to as network adapters [CML12, p. 16].

(c) Network on Chip (NoC)

Figure 2.1: Three communication infrastructures used in System-on-Chips.

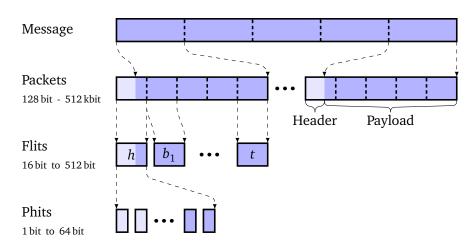

Figure 2.2: Data units at NoCs. The numbers underneath the left labels give ranges of typical sizes, according to [DT04, p. 225].

as a flow control scheme (cf. Section 2.4). Compared to off-chip networks, resources on a chip are constrained and routers share area and power budgets with other components. Consequently, NoC routers typically have limited buffering capacities. An overview of a typical router architecture is provided in Section 2.5.

#### Data units at NoCs

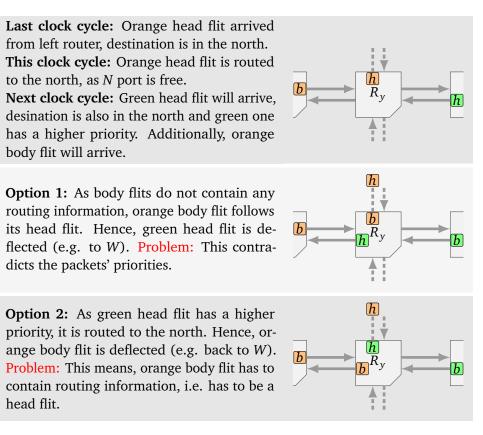

As mentioned before, the components of a NoC operate with different data units. An overview of the data units of NoCs is depicted in Figure 2.2. IP cores send and receive messages, e.g. cache lines, which can be arbitrarily long. The network interfaces create packets out of these messages. *Packets* usually have a restricted length, thus one message is divided into one or more packets. Additionally, a header is appended to each packet, which includes routing information. Packets are the basic unit of routing and sequencing, i.e. channels are allocated to packets. Depending on the switching technique, a packet may be further divided into flow control digits (flits). A flit is the basic unit of buffer and bandwidth allocation. The first flit of a packet is referred to as the head flit (herein denoted by h), which contains the packet's routing information. Depending on the packet's length, a head flit can be followed by several body flits (herein denoted by  $b_i$ ,  $i \in \mathbb{N}$ ) and at most one *tail flit* (herein denoted by t). As those flits carry no routing information, they have to follow the route of their head flit. Body and tail flits differ in that a tail flit deallocates the channel of the packet, which has been allocated by the head flit. In the case of a very short packet which consist of a single flit the head flit is also the tail flit. Figure 2.3 shows an example flit structure. Flits can be further divided into physical transfer digits (phits). A phit is the data unit that can be transmitted across a link in one clock cycle. Thus, if a flit is transferred as several phits, the flit is serialized

| Head flit: | ft=h | dst | src | hc | id | pl |

|------------|------|-----|-----|----|----|----|

| Body flit: | ft=b | pl  |     |    |    |    |

| Tail flit: | ft=t | pl  |     |    |    |    |

Figure 2.3: Flit structure of head, body, and tail flits. All flits contain a flit type field *ft* to distinguish between head, body, and tail flits, as well as a payload field *pl*. Head flits additionally contain a destination and source address field, *dst* and *src*, a hop count field *hc*, and an *ID* field *id*.

and deserialized at each transmission. In most cases, a flit corresponds to a phit and hence the flit size equals the link width.

In the following three sections, three essential aspects of NoCs are considered in more detail.

## 2.2 Topology

The topology of a NoC defines the network's structure, i.e. it specifies the way how routers are connected to each other. Therefore, the deployed topology affects many other aspects, as routing, achievable performance, reliability, and ease of layout. Topologies can be classified in different ways, and most of them are orthogonal to each other.

**Directness:** At direct topologies, the communication participants, referred to as components, sit inside the network. Every component is connected to a router and vice versa. The combination of a router and its connected component is referred to as a node. Thus, such networks are also known as router-based networks. At indirect topologies, the components sit outside the network. There, the components are connected by switches or switching elements, whereby some switches just forward messages, but they are not connected to any sender or receiver.

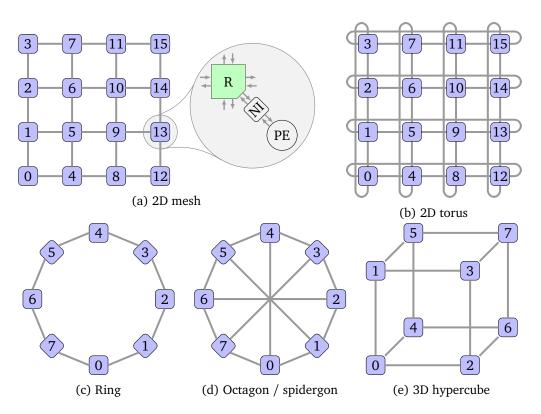

This section concentrates on direct topologies, which are most frequently utilized at NoCs. An overview of several direct topologies is depicted in Figure 2.4. The interconnection architecture inside a router architecture itself is usually based on an indirect topology. Thus, several indirect topologies are introduced in Section 2.5.

**Regularity**: A regular topology is defined in terms of a regular graph structure, such as a ring or a mesh. In some textbooks, a topology is defined to be regular if all nodes are identical in terms of their number of ports, e.g. in [DYL02, p. 14] and [QS13, p. 335]. Regular topologies are easier to analyze, whereas irregular topologies can be customized for a specific application. Already utilized irregular

Figure 2.4: Frequently used direct NoC topologies.

topologies are frequently composed of two regular topologies, e.g. a mesh of rings. Moreover, an irregular topology can arise if parts of the network fail.

**Symmetry:** At symmetric topologies, the network looks alike from every node.

Additionally to these fundamental attributes of topologies, they can also be compared by several theoretical metrics. Some important metrics are listed below.

- **Number of links**: The number of links is usually given as a function of N, whereas N denotes the number of nodes or routers in the network. Links provide bandwidth and hence, a higher number of links can increase the throughput and decrease the latency. On the other hand, a higher number of links increases the costs and can complicate the layout on-chip.

- **Radix:** The radix denotes a router's degree, i.e. its number of I/O ports. The costs of a router increase with its radix, as the number of buffers and arbiters, as well as the size of the router's interconnection architecture, increase with the radix.

- **Diameter**: The diameter of a topology gives the maximum distance between two nodes. Hence, the diameter is a lower bound of the maximum hop count<sup>3</sup>.

- **Average distance**: The average distance between two nodes influences the average hop count.

- **Bisection bandwidth:** The bisection bandwidth gives the number of links which have to break before the network is cut into two halves. At a higher bisection bandwidth, the blocking probability inside the network is lower.

Some popular and frequently utilized NoC topologies are briefly introduced below and pictured in Figure 2.4. The ring topology (cf. Figure 2.4c) requires only as many links as nodes are present in the network. Due to the small number of links, the average latency is  $\mathcal{O}(N)$  and the bisection bandwidth is constant. Thus, rings do not scale with a high number of nodes. However, hierarchical designs, as well as multi-ring designs, have been used to address the scalability of rings. The octagon topology (cf. Figure 2.4d) is another low-cost topology. It is based on a ring with eight nodes and additional links from each node to its diagonally opposite neighbor node. The spidergon topology is a generalization to an arbitrary but even number of nodes, which has been developed by STMicroelectronics [Cop+08]. The 2D mesh topology (cf. Figure 2.4a) is frequently utilized in commercial NoCs, e.g. in Tilera's Tile Processor family [Wen+07], as well as assumed in most scientific NoCs. It is a regular topology, easy to layout on-chip, and has links of equal length. Furthermore, it maps to the tiled CMP architecture naturally [BD06]. The path diversity and low average latency of  $\mathcal{O}(\sqrt{N})$  are additional advantages of this topology. Meshes are not symmetric on their edges, and thus the center of a mesh tends to be more congested. As a result, the performance of a node depends on its position in the network. The 2D torus topology (cf. Figure 2.4b) corresponds to a 2D mesh topology with additional connections at the edge nodes, which leads to a donut shape. Thus, a torus provides a higher path diversity and higher bisection bandwidth than a mesh topology. On the other hand, a torus has higher costs, is harder to layout onchip, and has unequal link lengths. However, the latter point can be solved by a folded torus, at which all links have the same length. The *n*-dimensional hypercube topology connects  $2^n = N$  nodes and provides a latency of  $\mathcal{O}(\operatorname{Id} N)$ . There, two processors are connected if and only if the binary representation of their labels differ at exactly one bit. Hypercubes were used in the past, e.g. in the Cosmic Cube [Sei85], as links were more expensive than routers. Values for the presented metrics and topologies are shown in Table 2.1.

<sup>&</sup>lt;sup>3</sup>The hop count of a packet denotes the number of nodes the packet has traversed.

|                       | Ring          | Spidergon <sup>a</sup> | $2D n \times n$       | $2D n \times n$       | <i>n</i> dim.              |

|-----------------------|---------------|------------------------|-----------------------|-----------------------|----------------------------|

|                       | Tung          |                        | mesh                  | torus                 | hypercube                  |

| Number of nodes       | Ν             | N = 4n                 | $N = n^2$             | $N = n^2$             | $N = 2^n$                  |

| Number of links       | Ν             | 1.5N                   | 2N-2n                 | 2N                    | $2^{n-1}n$                 |

| Router degree / radix | 2             | 3                      | 4                     | 4                     | ld(N)                      |

| Diameter              | $\frac{N}{2}$ | $\frac{N}{4}$          | $2\sqrt{N}$           | $\sqrt{N}$            | ld(N)                      |

| Avg. distance         | $\frac{N}{4}$ | $\frac{2n^2+2n-1}{N}$  | $\frac{2}{3}\sqrt{N}$ | $\frac{1}{2}\sqrt{N}$ | $\frac{\mathrm{ld}(N)}{2}$ |

| Bisection bandwidth   | 2             | 8                      | $\sqrt{N}$            | $2\sqrt{N}$           | $\frac{N}{2}$              |

<sup>a</sup>The depicted values correspond to N = 4n. Average distance and bisection bandwidth for N = 4n + 2 differ slightly from the depicted values. Exact values can be found in [Cop+08, p. 102].

Table 2.1: Metrics for different topologies. Values are given as a function of N, whereas N denotes the number of nodes in the network.

# 2.3 Routing

At almost all topologies, several paths between two nodes are available. The routing algorithm specifies how packets get from their source node to their destination node, i.e. which path is taken. Therefore, the utilized routing algorithm is a fundamental characteristic of a NoC, which affects the network's performance and correctness.

# 2.3.1 Classification

As topologies, routing algorithms can be classified in different ways and most of them are orthogonal to each other.

**Mechanism:** A routing mechanism which allows very simple routers, at the expense of larger headers, is *source based* routing. There, a source node specifies a packet's complete route throughout the network, which is stored in the packet's header.

At *lookup table based* routing, it is the other way round. A routing table is used to determine the output port for a given destination. This leads to larger routers but allows small packet headers.

Arithmetic based routing algorithms exploit the regularity of most NoC topologies. A simple arithmetic is used to determine the route throughout the network, e.g. approach the destination in x direction first.

**Type:** If always the same path between a source node and a destination node is chosen, a routing algorithm is referred to as *deterministic routing algorithm*. Such algorithms

are usually very simple and deadlock free, i.e. cycles at resource allocation are avoided. On the other hand, deterministic algorithms do not exploit the path diversity efficiently, which could lead to contention.

The goal of an *oblivious routing algorithm* is to balance the network load. However, the network state is not considered towards this end. An example is Valiant's algorithm [Val82], which randomly chooses an intermediate destination node, to which a packet is routed first. Thus, Valiant's algorithm routes packets along non-minimal paths to balance the network load.

If the algorithm adapts to the state of the network, it is referred to as an *adaptive routing algorithm*. Adaptive routing algorithms can be further classified as minimal or non-minimal algorithms<sup>4</sup>. *Minimal adaptive algorithms* use the network state, e.g. the capacity or utilization of downstream buffers, to select one productive output port<sup>5</sup>. *Non-minimal adaptive algorithms* can additionally misroute packets to non-productive output ports. The utilization of non-productive output ports can improve load balancing and network utilization. However, this also necessitates precautions against livelocks, as otherwise non-productive output ports could be selected infinitely. For instance, deflection routing (cf. Chapter 3) belongs to the group of non-minimal adaptive algorithms.

**Deadlock avoidance:** In general, deadlocks are caused by a circular dependency on resources. In particular, wormhole flow control (cf. Section 2.4) is susceptible to routing dependent deadlocks, at which a set of packets obstruct each other. Every packet of the set waits for a buffer or a link which is already occupied by another packet of the set. Figure 2.5 shows such a deadlock situation. One solution to avoid circular dependencies is to restrict the turns a packet can take. Glass and Ni developed the well-known turn model [GN92], which is briefly introduced below. Another solution to avoid routing dependent deadlocks is to use Virtual Channels (VCs). Finally, it is also possible to detect and break deadlocks, however, this requires buffer preemption.

### 2.3.2 Routing Algorithms and Turn Model

One of the most frequently deployed NoC routing algorithms, which is very simple, deterministic, minimal, and deadlock<sup>6</sup> free, is *dimension order routing*. There, packets are routed to their destination address along one dimension before they are routed along

<sup>&</sup>lt;sup>4</sup>More precisely, both deterministic and oblivious algorithms can be minimal as well as non-minimal. However, all herein considered deterministic routing algorithms are minimal, and all oblivious algorithms are non-minimal.

<sup>&</sup>lt;sup>5</sup>An output port or direction is referred to as *productive* for a packet if it brings the packet one hop closer to its destination node.

<sup>&</sup>lt;sup>6</sup>If not stated otherwise, the term deadlock hereinafter refers to a routing dependent deadlock.

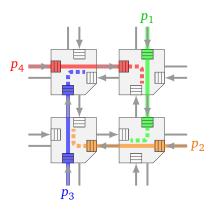

Figure 2.5: Routing dependent deadlock at a 2D mesh with input buffered routers. Packet  $p_1$  occupies right link (upper right router to lower right router) and needs bottom link. Packet  $p_2$  occupies bottom link and needs left link. Packet  $p_3$  occupies left link and needs top link. Packet  $p_4$  occupies top link and needs right link.

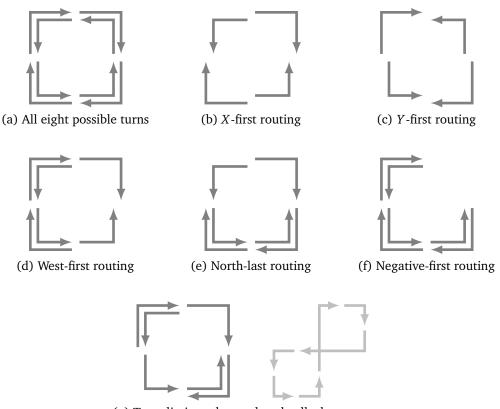

the next dimension. At a 2D mesh topology, packets are either routed along the x or the y direction before they are routed along the remaining direction. Depending on the direction which is chosen first, such a routing algorithm is referred to as X-first routing or Y-first routing<sup>7</sup>. Dimension order routing is deadlock free as the turns which a packet can take are restricted in a way that cyclic dependencies can not occur. Figure 2.6a shows all eight possible turns for a 2D mesh topology. These eight turns create two cycles, one in clockwise direction and one in counterclockwise direction. As shown in Figure 2.6b and Figure 2.6c, at both X-first routing and Y-first routing only four out of the eight possible turns are allowed, and thereby, both cycles are broken.

Restricting the number of turns is a simple and cost-effective solution to guarantee the abstinence of deadlocks. However, prohibiting more turns than necessary restricts the potential adaptiveness of a routing algorithm. Glass and Ni presented in [GN92] the well-known *turn model*. This model is herein explained for a 2D mesh, but the general concept can be extended to higher dimensional meshes as well as other topologies. Glass and Ni showed that a deadlock free routing algorithm for a 2D mesh can be created if exactly one turn in each of both cycles is prohibited. Furthermore, they found that only 12 ways, of the 16 possible ways to prohibit one turn in each cycle, prevent deadlocks. If symmetries are taken into account, three unique ways exist, each creating a deadlock free routing algorithm, as well as one way at which deadlocks can occur. The algorithms presented by Glass and Ni have in common that the north to west turn of the counterclockwise cycle is eliminated, as well as one turn in the clockwise cycle. However, any other turn instead of the north to west would be equally possible. The

<sup>&</sup>lt;sup>7</sup>They are also referred to as XY / YX routing as well as XY / YX dimension order routing.

(g) Two eliminated turns but deadlocks can occur

Figure 2.6: The turn model for a 2D mesh topology. Figure 2.6a shows all possible turns of a 2D mesh, Figures 2.6b to 2.6f show the allowed turns of the associated routing algorithms, and Figure 2.6g shows that not every combination of six turns results in a deadlock free routing algorithm.

first algorithm of the turn model is *west-first routing* (cf. Figure 2.6d). There, the south to west turn is prohibited in addition to the north to west turn. Hence, every packet has to be routed to the west direction first, as it can not turn to the west after it has turned to any other direction. The second algorithm is *north-last routing* (cf. Figure 2.6e), at which the north to east turn is prohibited in addition to the north to west turn. As a result, packets can not change their direction after heading to the north, and every packet has to be routed to any other direction before it is routed to the north. The third algorithm is *negative-first routing* (cf. Figure 2.6f). There, the east to south turn is prohibited in addition to the north to west turn is prohibited in addition to the north turn to the north turn to the north to the north to west turn. At negative-first routing, packets must be routed to the north and the east). The fourth turn which can be eliminated in the clockwise cycle is the west to north turn (cf. Figure 2.6g). However, as

depicted on the right of Figure 2.6g, eliminating this turn does not result in a deadlock free routing algorithm.

Chiu presented the odd-even turn model in [Chi00], which is an extension of Glass and Ni's turn-model. Depending on a router's position, different turns are prohibited to break the two cycles. In odd columns, the south to west turn and the north to west turn are prohibited. In even columns, the east to south turn and the east to north turn are not allowed. Compared to the original turn-model, the odd-even turn model provides a more even adaptiveness for different source-destination pairs.

# 2.4 Buffering and Flow Control

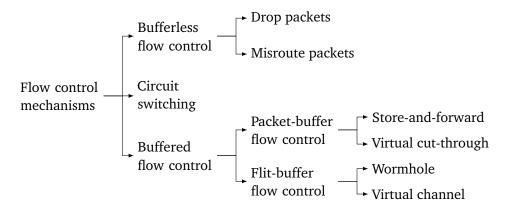

Besides the topology, which specifies the physical interconnection structure, and the routing algorithm, which specifies the set of paths a packet can follow, buffering and flow control are two further important aspects of NoCs. In general, buffering and flow control describes where data is stored within the network, how resources are allocated to packets traversing the network, and what happens if resources can not be allocated. Thus, flow control can be regarded as a problem of resource allocation as well as contention resolution [DT04, p. 221]. The resources to allocate include channel bandwidth, buffer capacity, and control state. A router's control state tracks the resource allocation within the router itself. A classification of NoC flow control mechanisms, presented by Dally and Towles in [DT04], is shown in Figure 2.7.

# 2.4.1 Bufferless Flow Control

*Bufferless flow control* is the simplest form of flow control. As no buffers exist, packets only have to allocate channel bandwidth and control state, but no buffer capacity. Consequently, packets can not be buffered in routers, i.e. they can not wait if an allocation

Figure 2.7: Classification of flow control mechanisms according to [DT04].

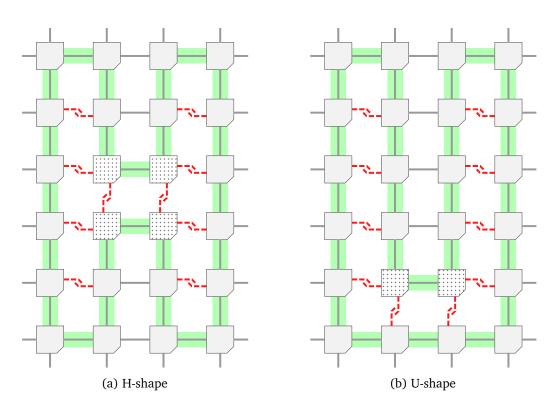

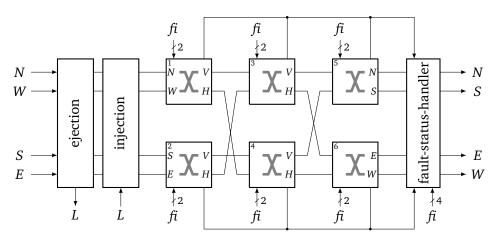

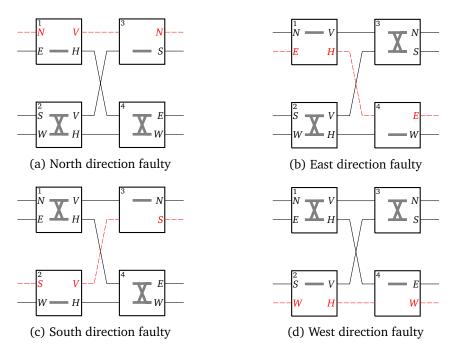

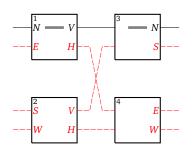

fails. There are two options to deal with a packet whose attempt to allocate its required resources failed. Such a packet can either be *dropped* or *misrouted*. In the case of packet dropping, packets which are dropped later waste bandwidth. Furthermore, a retransmission scheme is required. Misrouting does not drop packets, but sends them to non-productive directions instead. Thus, misrouting is susceptible to livelocks and a guarantee that every packet gets delivered eventually is needed. Misrouting is also referred to as *deflection routing* or *hot-potato routing*, and has been proposed by Baran in [Bar64]. Deflection routing is introduced in more detail in Chapter 3.