# Fabrication of magnetic artificial atoms

### Dissertation

zur Erlangung des naturwissenschaftlichen Doktorgrades der Julius-Maximilians-Universität Würzburg

vorgelegt von Radu-Gabriel Dengel aus Slatina

Würzburg 2013

### Eingeeicht bei der Fakultät für Physik und Astronomie

### Gutachter der Dissertation:

- 1. Gutachter: Prof. Dr. Laurens W. Molenkamp

- 2. Gutachter: Prof. Dr. Bert Hecht

### Prüfer im Promotionskolloquium:

- 1. Prüfer: Prof. Dr. Laurens W. Molenkamp

- 2. Prüfer: Prof. Dr. Bert Hecht

- 3. Prüfer: Prof. Dr. Reinhold Oppermann

## Parts of this thesis have been published elsewhere

- R.-G. Dengel, A. Frey, K. Brunner, C. Gould, L. W. Molenkamp, *Fabrication of magnetic artificial atoms*, Nanotechnology **23**, 395301 (2012)

- A. Frey, M. Ruth, R.-G. Dengel, C. Schumacher, C. Gould, G. Schmidt, K. Brunner, L. W. Molenkamp, Semimagnetic II-VI semiconductor resonant tunneling diodes characterized by high-resolution X-ray diffraction, Journal of Crystal Growth 312, 1036 (2010)

# Contents

| Zusammenfassung Summary |                                                                   |        |                                          |  |       |  |  |   |

|-------------------------|-------------------------------------------------------------------|--------|------------------------------------------|--|-------|--|--|---|

|                         |                                                                   |        |                                          |  |       |  |  | 1 |

| 2                       | State of the art quantum dots and diluted magnetic semiconductors |        |                                          |  |       |  |  |   |

|                         | 2.1                                                               |        |                                          |  |       |  |  |   |

|                         | 2.2                                                               | The II | I-VI material system                     |  | . 18  |  |  |   |

|                         |                                                                   | 2.2.1  | (Zn,Be,Cd,Mn)Se semiconductor alloy      |  | . 18  |  |  |   |

|                         |                                                                   | 2.2.2  | Diluted magnetic semiconductor (Zn,Mn)Se |  | . 20  |  |  |   |

|                         | 2.3                                                               | Quant  | tum well energy adjustment               |  | . 23  |  |  |   |

|                         |                                                                   | 2.3.1  | Width variation                          |  | . 25  |  |  |   |

|                         |                                                                   | 2.3.2  | Bandgap variation                        |  | . 27  |  |  |   |

| 3                       | Contacting                                                        |        |                                          |  |       |  |  |   |

|                         | 3.1                                                               | Conta  | act separation                           |  | . 31  |  |  |   |

|                         | 3.2                                                               | Top co | contacting                               |  | . 42  |  |  |   |

|                         |                                                                   | 3.2.1  | Fabrication of line mesas                |  | . 42  |  |  |   |

|                         |                                                                   | 3.2.2  | Applicability of line mesas              |  | . 49  |  |  |   |

|                         |                                                                   | 3.2.3  | Air-bridge technique                     |  | . 53  |  |  |   |

| 4                       | Pilla                                                             | Pillar |                                          |  |       |  |  |   |

|                         | 4.1                                                               | Pillar | mesa fabrication                         |  | . 61  |  |  |   |

|                         | 4.2                                                               | Result | ts of pillar mesa miniaturization        |  | . 74  |  |  |   |

| 5                       | Gate technology                                                   |        |                                          |  |       |  |  |   |

|                         | 5.1                                                               | Insula | ator                                     |  | . 81  |  |  |   |

|                         | 5.2                                                               | Gating | g technique                              |  | . 86  |  |  |   |

|                         |                                                                   | 5.2.1  | Gate designs and fabrication             |  | . 86  |  |  |   |

|                         |                                                                   | 5.2.2  | Gate performance                         |  | . 97  |  |  |   |

| 6                       | Magnetic artificial atoms 10                                      |        |                                          |  |       |  |  |   |

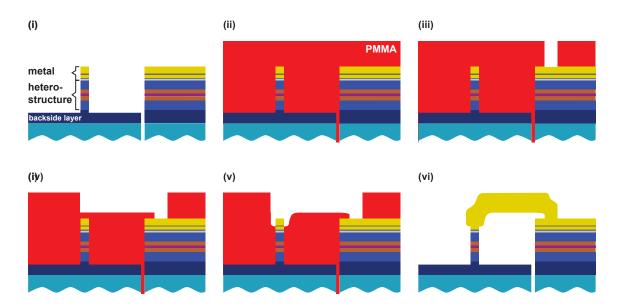

|                         | 6.1                                                               | Manuf  | facturing processes                      |  | . 105 |  |  |   |

|                         |                                                                   | 6.1.1  | Basic vQDot process                      |  | . 106 |  |  |   |

vi Contents

|              | 6.2                               |                           | Improved vQDot process               |     |  |  |  |

|--------------|-----------------------------------|---------------------------|--------------------------------------|-----|--|--|--|

| 7            | Con                               | onclusion and Outlook 131 |                                      |     |  |  |  |

| $\mathbf{A}$ | Artificial magnetic atoms gallery |                           |                                      |     |  |  |  |

| В            | Alte                              | ernativ                   | ve bridge technology for nanopillars | 141 |  |  |  |

| $\mathbf{C}$ | C.1                               |                           | ecipes process                       |     |  |  |  |

| Bi           | bliog                             | graphy                    |                                      | 167 |  |  |  |

Die Fabrikation und Erforschung künstlicher Atome ist hinsichtlich ihres physikalischen Verständnisses und ihrer Herstellungstechnologie weit fortgeschritten. Diese werden vorwiegend in lateralen oder vertikalen Quantenpunkten (QDots) aus dem III-V Materialsystem erzeugt. Allerdings ist es derzeit nicht möglich, künstliche Atome mit ausgeprägten magnetischen Eigenschaften herzustellen, um diese zu untersuchen. Diese Arbeit präsentiert die Punkt-für-Punkt-Entwicklung der Herstellungstechnologie sowie erste experimentelle Beobachtungen von künstlichen magnetischen Atomen aus dem II-VI verdünnt magnetischen Halbleitermaterialsystem (Zn,Cd,Be,Mn)Se. Das der Entwicklung zugrunde liegende elektronische Bauelement ist eine resonante Tunneldiode (RTD) aus dem II-VI Halbleitermaterialsystem, die früher bereits entwickelt wurde.

Auf der Basis des konstanten Wechselwirkungsmodells, das zur Beschreibung von künstlichen Atomen herangezogen wird, sowie der Giant-Zeeman Energieaufspaltung im paramagnetischen Quantentrog (QW) (Zn,Cd,Mn)Se der Doppelbarrierenstruktur wird die Entstehung künstlicher Atome mit starken und interessanten magnetischen Eigenschaften erwartet. Aus Experimenten an künstlichen Atomen ist bekannt, dass es am besten ist, die RTDs, aus denen die Quantenpunkte hergestellt werden, im linearen Transportbereich um  $U_{SD} \approx 0$  V zu betreiben. Die Ausgangs-II-VI RTD, mit einer QW-Breite von 7 nm, hat ihre erste Resonanz, aufgrund der großen Energieabstände in der  $k_z$  Quantisierung erst bei 160 mV. Da diese Energiegrößenordnung nicht mit einer Steuerungselektrode (Gate) manipuliert werden kann, ist es notwendig, die Resonanz von vornherein physikalisch in die Nähe der Fermienergie der Kontakte zu bringen. Als erstes wird die QW-Breite erhöht, die jedoch die Resonanz deutlich verbreitert aber ihre Position auf der Spanungsskala nicht weit genug erniedrigt. Die Erniedrigung der Position bis auf 0 V wird stattdessen über die Verkleinerung der Bandlücke im 7 nm breiten QW durch das Hinzufügen von  $\sim 7.6\%$  Cd erreicht.

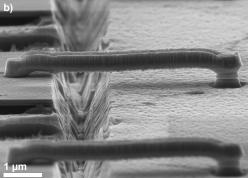

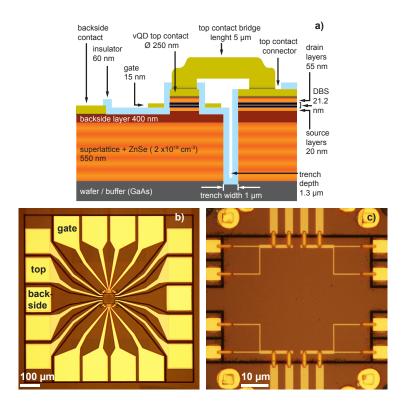

Die II-VI RTD wird pseudomorph auf einem GaAs Substrat gewachsen. Elektrische Felder und die Aufladung der III-V/II-VI Grenzfläche verhindern die Verwendung der Substratrückseite als einen Rückseitenkontakt des Bauelements. Diese Eigenschaft stellt neue Anforderungen an die Kontaktanordnung des RTD-Bauelements. Aufgrund der durchgehenden, hochdotierten Rückseitenschicht müssen die Topkontakt-, Rückseitenund Gatekontaktbondelektrode voneinander physikalisch getrennt werden, um einen eindeutigen Strompfad durch die Struktur festzulegen. Es wird deshalb ein zuverlässiger und Oberflächen nichtkontaminierender Herstellungsprozess für  $\geq 1,3~\mu{\rm m}$  tiefe Trenngräben entwickelt. Er basiert auf dem Aufbringen von 100 nm Ti als Maske während des

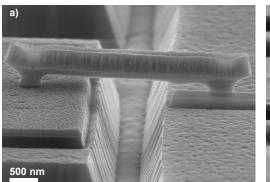

Trockenätzprozesses, die sich anschließend problemfrei entfernen lässt. Darüber hinaus müssen Methoden zur Topkontaktierung des submikrometer breiten Türmchens ausgelotet werden, da eine direkte Kontaktierung mit dem Drahtbonder nicht möglich ist. Das Linienmesaprinzip, das von Austing et al. [Aust 96] entwickelt wurde und nun standardmäßig in III-V (QDots) verwendet wird, wird auf seine Anwendbarkeit in der II-VI RTD getestet. Da 200 nm breite Linien immer noch elektrisch leitfähig sind, kann diese Methode nicht verwendet werden. Die Brückentechnologie ist deshalb weiterhin die Methode der Wahl, muss allerdings hinsichtlich der PMMA-Lackdicke angepasst werden, um ein Überbrücken der tiefen Trenngräben zu gewährleisten.

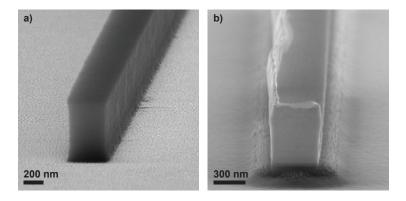

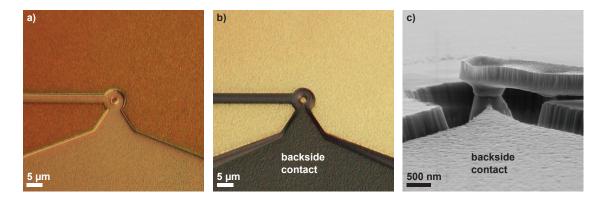

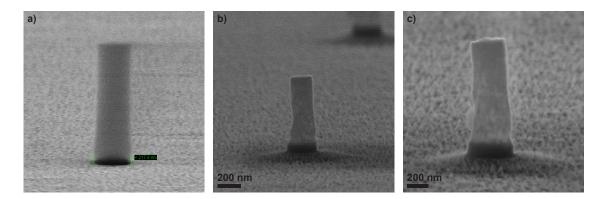

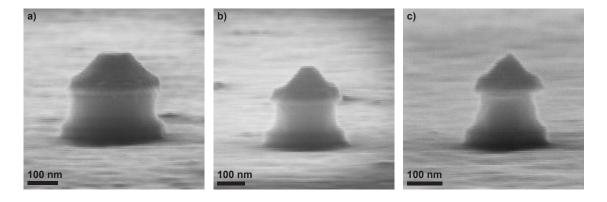

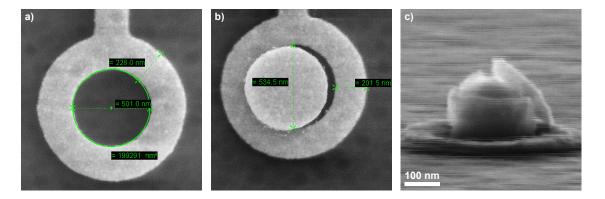

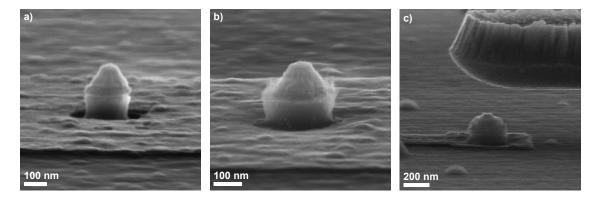

Aus den gewonnenen Erkenntnissen während der Entwicklung des Herstellungsverfahrens für die Linien, ist der Prozess zur Verkleinerung der Türmchendurchmesser hin zu submikrometer Abmessungen erfolgreich entwickelt und angewendet worden. In diesem Zusammenhang wird wieder eine Ti-Trockenätzmaske mit einer Dicke von 60 nm zum Trockenätzen von 250 nm hohen Türmchen verwendet. Dem Ar-Ionenstrahl wird BCl<sub>3</sub> als chemische Komponente hinzugefügt. Weiterhin verhindert ein geringerer Einfallwinkel die Ausbildung von Ätzgräben und erzeugt steilere Seitenwände an den Türmchen. Dieses Grundherstellungsverfahren für künstliche Atome beinhaltet das Entfernen des überschüssigen Ti mittels Flusssäure. Abweichungen in den physikalischen Eigenschaften unterschiedlicher Substrate haben zu einer Weiterentwicklung dieses Prozessschrittes geführt. Dabei wird das überschüssige Ti der Trockenätzmaske ausschließlich trockenchemisch entfernt. Die so hergestellten Strukturen werden elektrisch bei 4,2 K getestet und weisen einen zunehmenden Einfluss der Quantisierung durch die laterale Abnahme der Abmessungen auf.

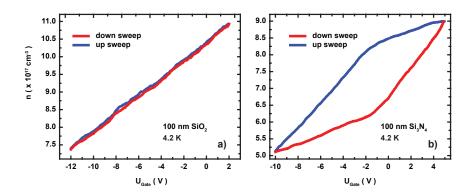

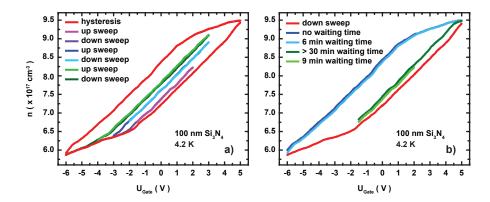

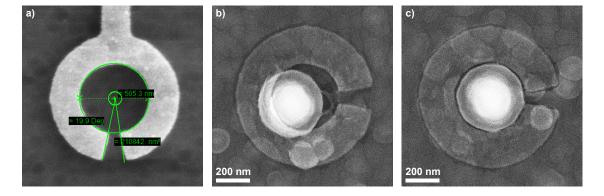

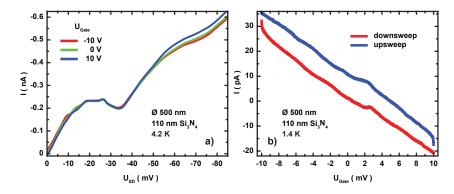

Nachdem ein zuverlässiges Herstellungsverfahren für Submikrometertürmchen mit Abmessungen bis herunter zu 200 nm Durchmesser entwickelt wurde, wird das wichtigste Element, das Gate, das die Untersuchung der elektrischen Eigenschaften der QDots erlaubt, hinzugefügt. Die Unterschiede zwischen dem III-V und II-VI Materialsystem hinsichtlich der Bauteilhöhe, Schichtabfolge, des Einflusses von Atzchemikalien und des Nichtvorhandenseins eines idealen Schottky-Kontakts erfordern die Entwicklung eines geeigneten Designs sowie Herstellungsprozesses des Gates. Außerdem zeigt die Untersuchung der elektrischen Eigenschaften der mittels PECVD konform aufgebrachten Dielektrika, dass mit Si<sub>3</sub>N<sub>4</sub> eine größere Ladungsträgermanipulation möglich ist, aber die auftretende Hystherese ebenfalls nicht zu vernachlässigen ist. Da das Gate nicht mittels selbstlimitierenden Schattenaufdampfens aufgebracht werden kann, wird das Gate mit dem Elektronenstrahl definiert. Hierzu ist eine hohe Präzision unter Berücksichtigung systematischer Abweichungen bei der Ausrichtung erforderlich. Eine Weiterentwicklung zu einem flächigen Gate erhöht zwar die Komplexität des Herstellungsverfahrens, aber durch das Verwenden einer schützende Lackmaske kann das überschüssige Metall auf der Türmchenspitze entfernt werden. Allerdings löst die neue Methode die Schwierigkeiten mit der Ausrichtung. Die vertikale Ausrichtung des Gates wird erreicht, indem die Ätzraten und -tiefen des Halbleiters sowie Aufbringraten und -dicken des Dielektrikums sorgfälltig überprüft werden. Die elektrischen Messungen an den so hergestellten Bauteilen zeigen, dass das Verfahren funktioniert. Allerdings werden im Falle einer Falschpositionierung auch die

daraus resultierenden Einflüsse sichtbar.

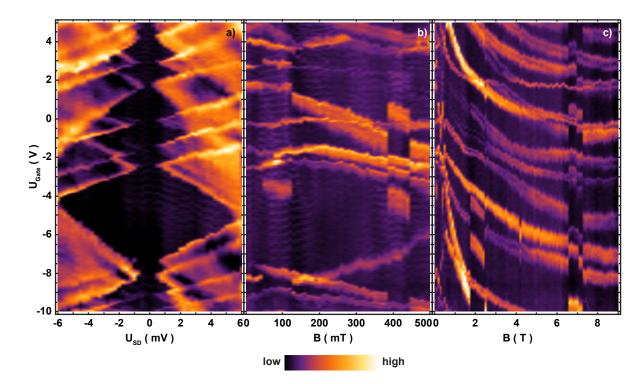

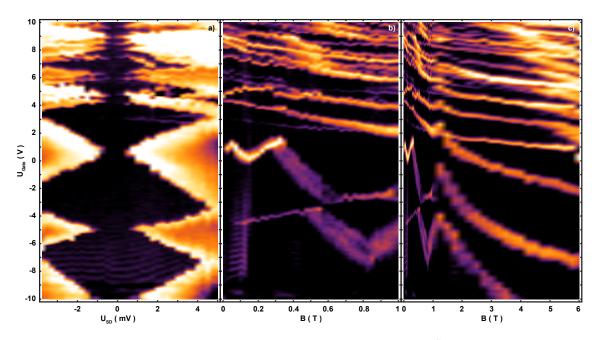

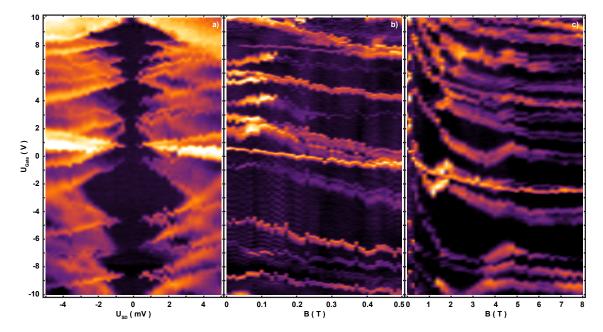

Abschließend wird der komplette Herstellungsprozess von Anfang bis Ende, wie in [Deng 12] vorgestellt, präsentiert. Das Grundherstellungsverfahren wird mit dem verbesserten und universelleren Herstellungsprozess ergänzt. Der Letztere enthält Veränderungen, die die Herstellung flexibler auf Abweichungen reagieren lassen. Der verbesserte Herstellungsprozess entkoppelt das Verfahren vom II-VI Materialsystem, so dass er auf andere Materialsysteme ebenfalls angewendet werden kann. Tieftemperaturmessungen, an einem 250 nm breiten Türmchen aufgezeichnet, zeigen die Ausbildung von QDots. Die hohen Widerstände des Bauteils haben allerdings Ströme zur Folge, die vergleichbar zu den Leckströmen durch den Isolator sind. Aus diesem Grund müssen die DC-Messungen durch Lock-in Messungen ersetzt werden. Hierbei wird eine kleine AC-Anregungsspannung bei niedrigen Frequenzen hinzugefügt. Die niedrigen Frequenzen verhindern ein kapazitives Leck. Darüberhinaus weisen die Messungen von Coulomb-Oszillationen bei unterschiedlichen Anregungsspannungen sowie das Stabilitätsdiagramm das Vorhandensein einer Blockade in Serie mit dem QDot auf. Außerdem deuten die aufgezeichneten Fock-Darwin-Spektra auf die Enstehung von mehreren QDots hin, da Spektra überlagert sind. Trotzdem kann man eine ausgeprägte paramagnetische Komponente beobachten. Beim Anlegen eines Magnetfeldes ändert sich die Position der Energieniveaus entsprechend einer Brillouin-Funktion. Dies belegt die ausgeprägten magnetischen Eigenschaften im QDot. Durch die zusätzlich beobachtete  $k_x$ - $k_y$  Quantisierung wird die Entstehung von künstlichen magnetischen Atomen belegt. Aufgrund der Bauteilunzulänglichkeiten können keine quantitativen Schlüsse gezogen werden. Das Verhalten des Bauteils entspricht jedoch dem berechneten Spektrum, zusammengesetzt aus dem konstanten Wechselwirkungsmodell und der Giant-Zeeman Energieaufspaltung im II-VI Halbleiter. Insgesamt führt die Aufspaltung dazu, dass eine Spinausrichtung mit zunehmendem Magnetfeld dominiert. Dies unterstreicht nochmals den paramagnetischen Charakter der künstlichen Atome.

The study and fabrication of artificial atoms, consisting of lateral or vertical quantum dots (vQDots), primarily from the III-V material system, are well advanced in understanding and technology. However, to date the field lacks the capability to create and investigate artificial atoms with pronounced magnetic properties. This thesis presents a detailed technology development of the fabrication process and first experimental observations of artificial magnetic atoms based on a previously established resonant tunneling diode (RTD) heterostructure from the II-VI diluted magnetic semiconductor (DMS) alloy (Zn,Cd,Be,Mn)Se.

From the constant interaction model describing artificial atoms, and the Giant-Zeeman energy splitting in the paramagnetic (Zn,Mn)Se quantum well (QW) of the double barrier heterostructure (DBH), the formation of artificial atoms with a strong and exciting magnetic response is expected. As is known, the best regime to operate the RTD devices forming the vQDot is in linear transport at source-drain bias voltages of  $U_{SD} \approx 0$  V. However standard II-VI RTD heterostructure with a QW of 7 nm exhibits the first resonance at bias voltages of about 160 mV, due to the large energetic spacings in the  $k_z$  quantization. Since this energy scale cannot be reasonably addressed by gate, it is necessary to physically lower the energy levels down to the vicinity of the Fermi energy of the leads. The first attempt is done by increasing the QW width, which adds significant broadening but does not lower the resonance enough. Instead the reduction of the 7 nm QW's energy bandgap by the incorporation of  $\sim 7.6\%$  Cd is shown to be the correct approach to line up the QW's energy level with the contacts Fermi level.

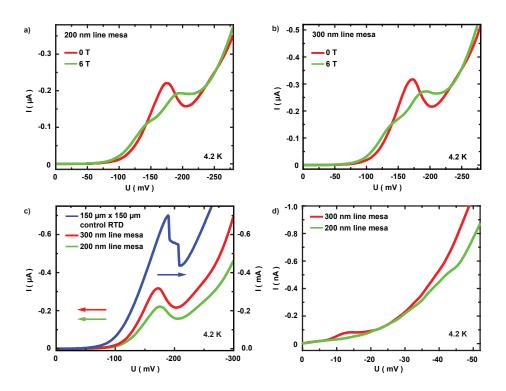

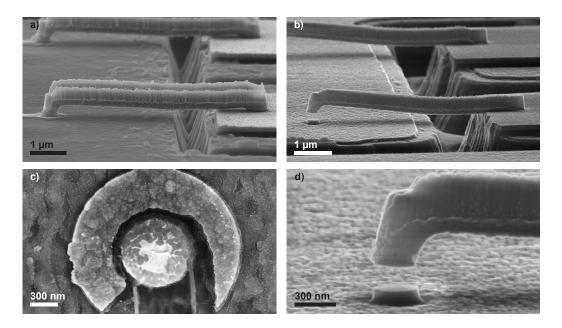

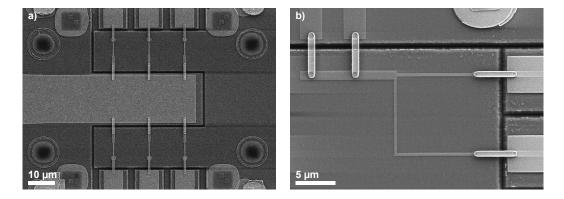

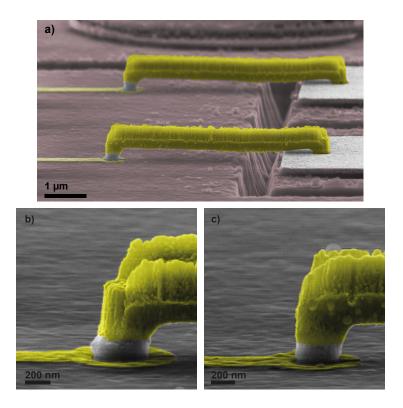

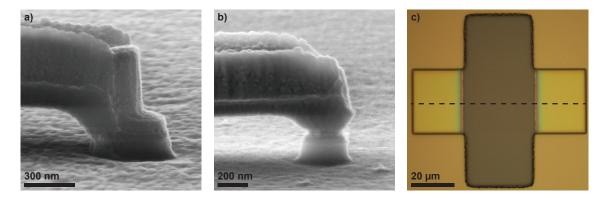

The II-VI RTD heterostructure has to be grown pseudomorphic on a GaAs wafer. Electrical fields as well as the charging at the III-V/II-VI interface prevent the use of the wafer backside as a real backside contact and therefore impose new challenges to the contacting scheme of the RTD devices. Because of the continuous highly doped backside layer, the top contact, backside and gate bonding pads requires physical separation of the different contact areas to ensure a well defined current path through the device. Therefore a reliable, easily removable and surface non-contaminating fabrication process for  $\geq 1.3~\mu m$  deep separating trenches is developed based on a 100 nm thick Ti metal mask and dry etching. Also, since submicron pillar dimensions eliminate the possibility of wire bonding the top contact, alternative techniques have to be exploited. The state of the art line mesa method presented by Austing et al. [Aust 96] is tested for the II-VI RTD heterostructure. However 200 nm lines are still fully conductive and prove this method to be not applicable to the II-VI devices. An air-bridge technique therefore is

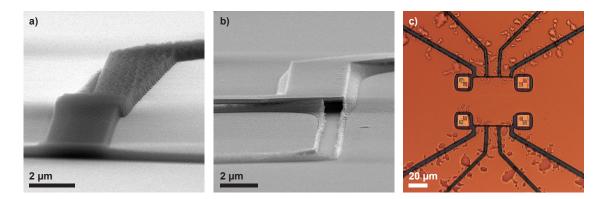

the appropriate top contact method, but it requires some adjustments in the resist layer composition in order to facilitate bridging across the deep and narrow trenches.

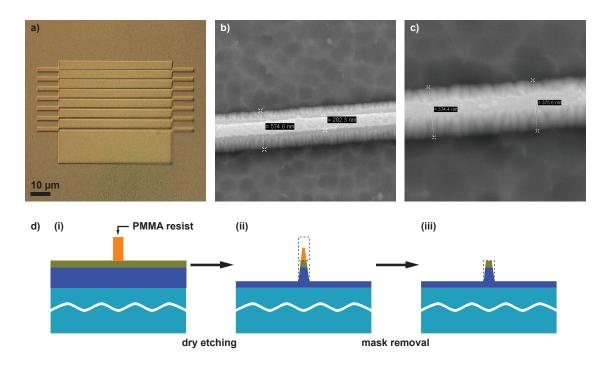

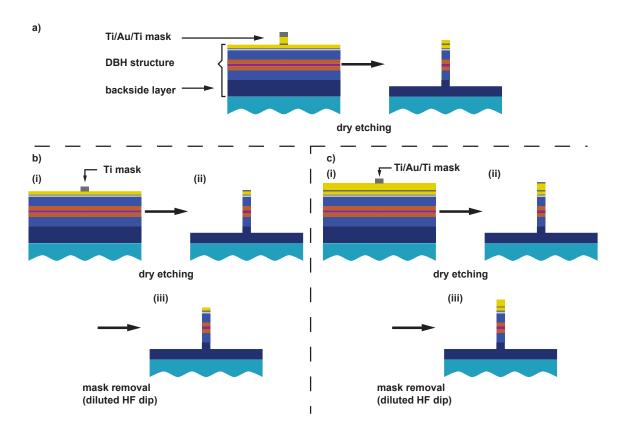

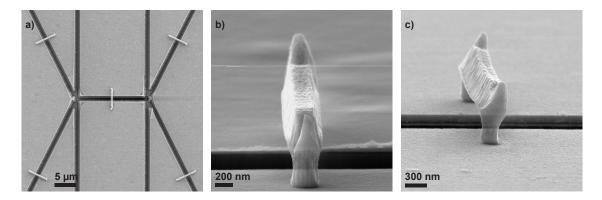

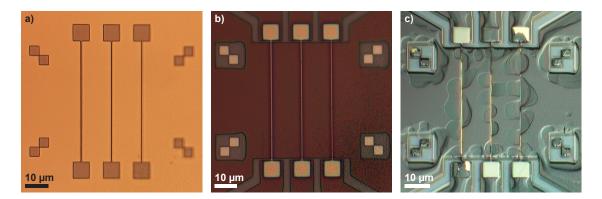

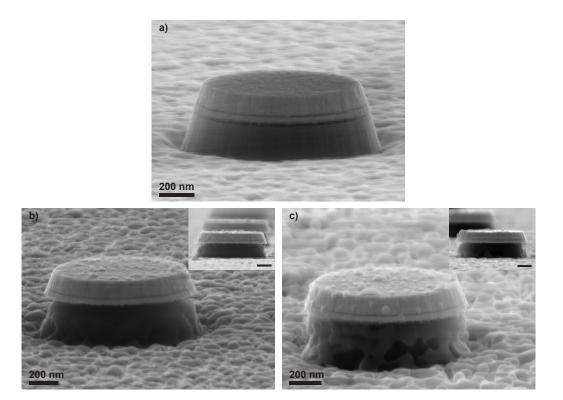

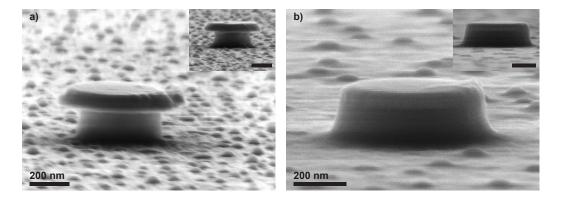

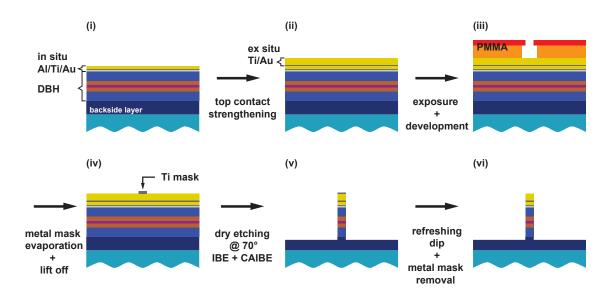

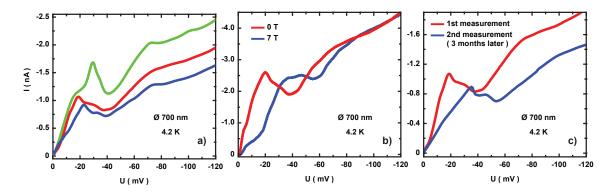

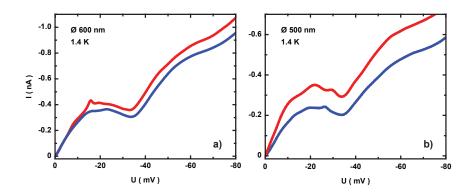

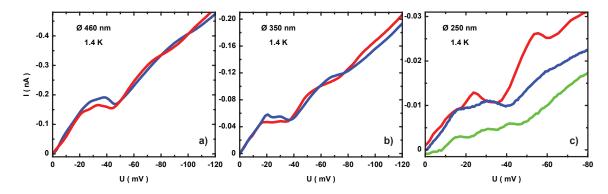

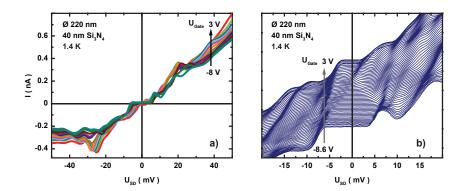

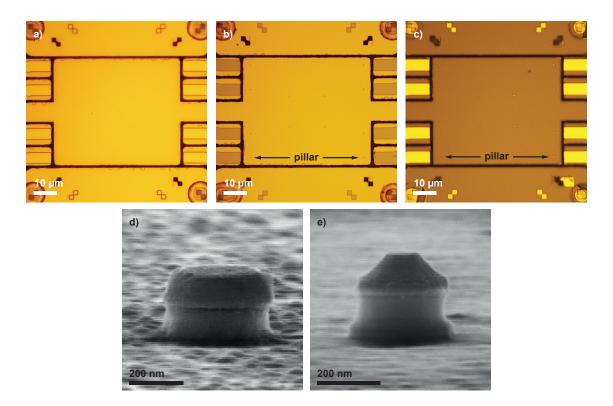

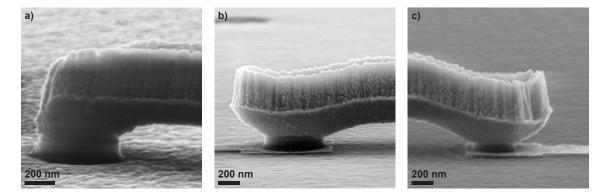

From the insights gained on developing a reliable manufacturing method of the submicron line mesas, the RTD pillar width is successfully reduced to submicron dimensions. Once again a  $\sim 60$  nm thick Ti metal dry etching mask is used to fabricate the 250 nm high pillars by using BCl<sub>3</sub> in chemical assisted ion beam etching with argon. Decreasing the incident etching angle steepens the pillar's sidewalls and prevents the formation of etching trenches around it. The developed process, which is part of the basic fabrication process for artificial atoms, involves hydrofluoric acid to remove the excess Ti mask. Variations in the physical properties of different RTD wafers have led to a further development of this step, which now only involves dry etching and a protective resist mask for the excess Ti removal in the end. Electrical characterization, at liquid helium temperature, of the fabricated devices show increasing influence from the lateral confinement through lateral miniaturization of the pillar dimensions.

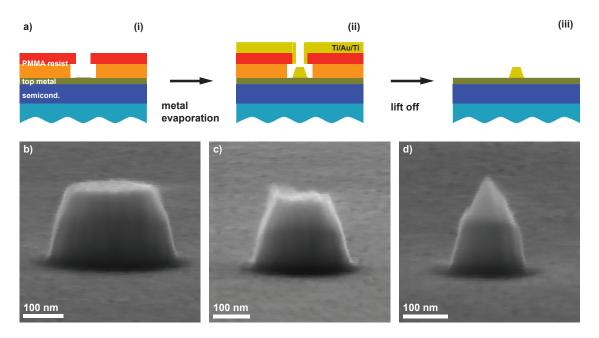

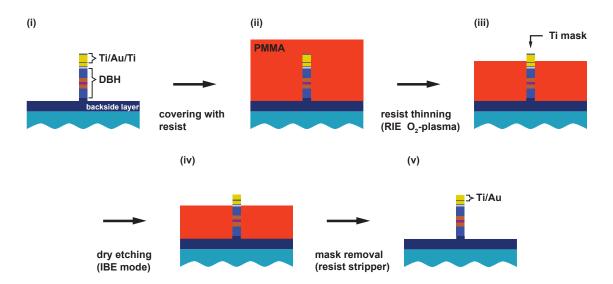

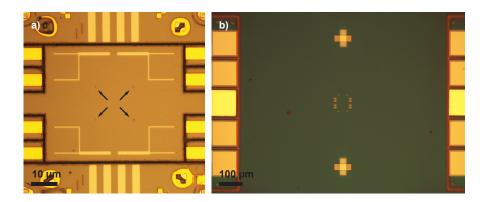

With a reliable manufacturing process of nano-pillars for working diameters as small as 200 nm, the most important element in the investigation of the electronic properties of the vQDots is now addressed: the application of a gate electrode. The differences between the III-V devices and the II-VI material system in vertical dimensions, the layer sequence, impact of wet etchants and especially the non-availability of ideal Schottky contacts require the development of a suitable design and fabrication process for the gate electrode. Investigating the electric properties of conformal deposited SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> by plasma enhanced chemical vapor deposition reveals that Si<sub>3</sub>N<sub>4</sub> provides the higher gating effect, but also exhibits a non-negligible hysteresis. The absence of a shadow masking technique for self aligning the gate requires defining the gate electrode by electron beam lithography. This requires high precision horizontal alignment of the gate by carefully accounting for systematic shifts in the electron beam lithography step. Further development leading to a plane gate method adds extra steps to the complex fabrication process, by once again using a protective resist mask to remove metal on the pillars insulator-covered top contact. Nevertheless this method helps in overcoming issues from unavoidable misalignments. The vertical alignment to the very narrow positioning window is achieved by carefully monitoring of semiconductor etching rates and depths as well as dielectric deposition rates and thicknesses. Electrical characterization measurements prove, on the one hand, the suitability of the method, and on the other hand, reveal influences from vertical misalignment of the gate electrode.

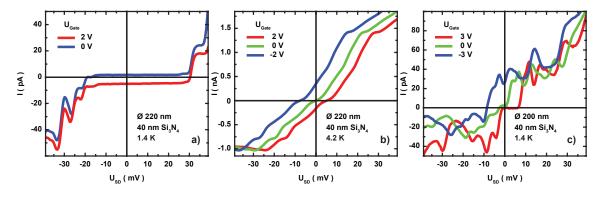

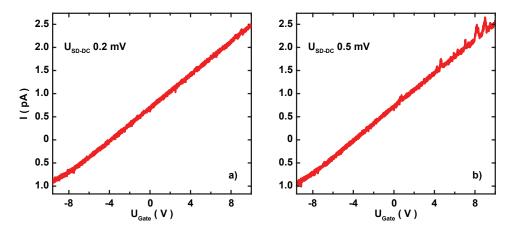

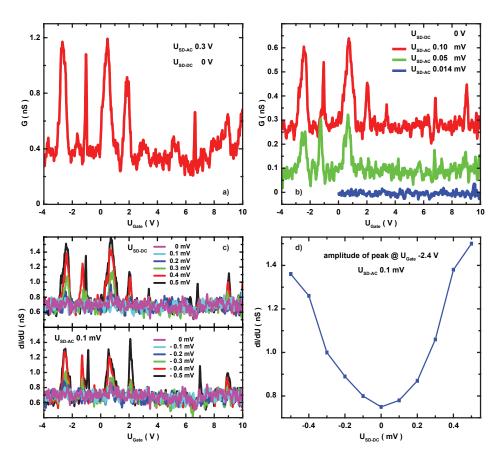

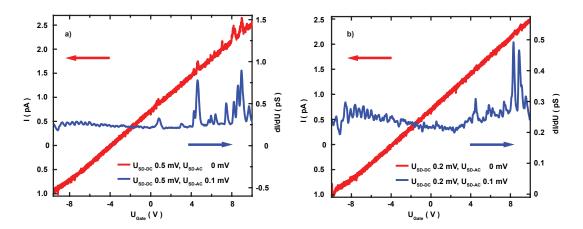

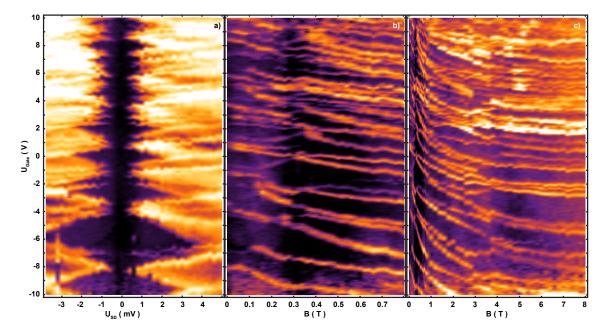

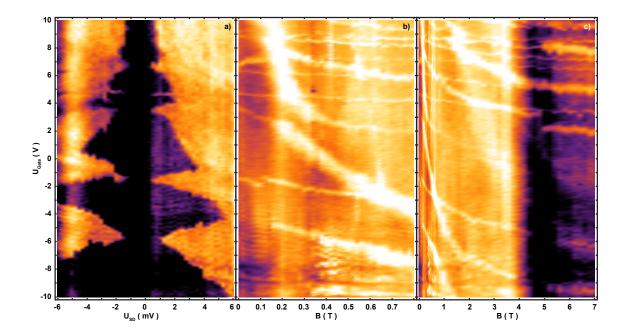

Finally the entire fabrication process from beginning to end, as presented in [Deng 12], is described in detail. This basic fabrication process is supplemented with the improved and more universally applicable manufacturing process that contains the modifications necessary for enhanced versatility in fabrication. Generally speaking the improved process decouples the fabrication from the specific II-V semiconductor alloy used in the work, and makes it easily portable to other material systems. Low temperature characterization measurements recorded in a dilution refrigerator on a 250 nm diameter pillar show the formation of vQDots. The high resistance of these devices leads to currents at  $U_{SD} \approx 0$  V of similar order as the leakage current through the dielectric. Thus pure DC mea-

surements have to be replaced by Lock-in experiments, where a smaller AC excitation is added at low frequencies. The later helps to avoid capacitive leakage from the leads. Additionally Coulomb oscillation measurements at different bias voltages and the stability diagram indicated the presence of an extra blockade in series with the formed QDot. The recorded Fock-Darwin spectrum suggest the formation of more than one QDot leading to the observation of superimposed spectra. Nevertheless, a clear and strong paramagnetic component is observable. The Brillouin characteristic of the evolution of the quantized levels in a magnetic field proves the strong magnetic response present in the quantum dot. Together with the clear observation of the  $k_x$ - $k_y$  quantization this documents the observation of artificial magnetic atoms. Quantitative findings can however not be extracted from the measurements, due to device imperfections. The behavior qualitatively corresponds to the calculated spectrum of a constant interaction model supplemented with the Giant-Zeeman energy splitting in the II-VI semiconductor. Altogether this leads to a quick domination of the spin-down energy levels as the magnetic field increases, underlining the paramagnetic nature of the artificial magnetic atom.

# Chapter 1

## Introduction

Beginning with Democritus, who first expressed and developed the idea of atoms as the smallest unbreakable parts of matter, mankind's interest in the elements of our physical world and the laws of their interaction has always remained undiminished. For centuries more and more secrets have been revealed and a comprehensive picture of these building blocks of matter has been gained. Nevertheless some properties of real atoms still can't be studied with the methods on hand due to their physical limitations. To give an example, the electronic 'singlet-triplet' transition of a helium atom as a function of the magnetic field requires several 10<sup>5</sup> Tesla [Thur 82], which are not accessible in any manmade system. Therefore the availability of structures with qualitatively similar physical properties, which however are much more easily accessible, would enable the study of novel physical properties.

In 1986 Watanabe and Inoshita [Wata 86] proposed the novel concept of artificial atoms from a modulation doped III-V semiconductor heterostructures, which they called 'superatoms' at first. Their semi-classical calculations together with Inoshita's *et al.* work [Inos 86, Inos 88] show the formation of well-defined atomic orbitals within the proposed system. However, the formation of artificial atoms proved to be most feasible by the fabrication of quantum dots. These are comparable to small boxes, whose dimensions are of the order of the de Broglie wavelength of the electrons. The 3D confinement of the electron wave gives rise to the emergence of discrete energy levels which resemble atomic orbitals in real atoms.

In order to investigate the electronic transport properties of such QDots one must attach leads to these 0D objects. Thus two possibilities for device configurations are the lateral design, where the leads are attached laterally, or the vertical design, where the QDot is sandwiched between the source and drain contacts. The work of Meirav *et al.* [Meir 90] on narrow interrupted channels into a GaAs/AlGaAs 2DEG facilitated for the first time to the observation of Coulomb blockade in an artificial system. Further improvement of the design led then to the realization of fully tunable lateral QDots [Goul 98, Cior 00]. In contrast, the pioneering work of Esaki, Tsu and Chang [Esak 58, Chan 74] and the progress in molecular beam epitaxy (MBE) resulted in a novel type of devices: the resonant tunneling diodes (RTD). With their double barrier heterostructure (DBH) they

1. Introduction

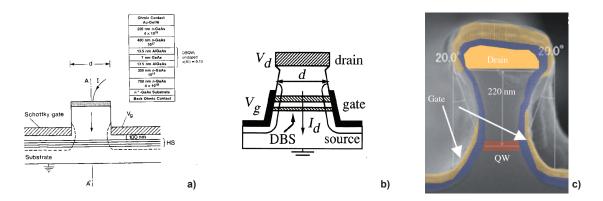

already provide a quantization of the energy in the growth direction. Advances in micro and nano lithography enabled the lateral downscaling of RTDs with properly tunned bandstructure to the region of lateral quantum confinement [Reed 88, Su 91, Tewo 92]. Moreover the addition of a gating electrode [Kina 90, Dell 92a] allows for further manipulation of the bandstructure [Guer 92a, Bent 92, Wang 94b]. A direct control over the lateral quantum confinement in these submicron RTD devices thus leads to a direct influence on the energy levels and the formation of vertical quantum dot (vQDot).

In 1995 Tarucha et al. [Taru 95] reported on the fabrication of a single electron transistor from a side-gated GaAs/AlGaAs RTD, which allowed the observation of irregular Coulomb blockade oscillations. This design was then used for devices with an optimized AlGaAs/InGaAs DBH in 1996 [Taru 96]. Inside these 0.5  $\mu$ m wide circular pillars a 2D disk shaped dot is formed from the lateral confinement of the few-nm thick quantum well. The confinement potential of this disk is best approximated by a two-dimensional harmonic potential which gives rise to degenerate sets of single-particle states. The analysis of the Coulomb oscillations' spacings in the absence of a magnetic field confirms the energetic degeneracies in the QDot and each set of levels can be regarded as a shell. Furthermore a close investigation of the peak spacings for half-filled shells reveals that electrons are added to the QDot following Hund's first rule. These findings reveal that the electronic spectrum in these vQDots represents an analogy to the one of real atoms and that the QDots can be regarded as artificial atoms. Over the last decade, these artificial atoms and the tunability of their electronic properties offered thus a suitable lab environment to test electronic, magnetic or spin related phenomena [Kouw 01, Reim 02, Hans 07] in single or multiple QDots.

Nevertheless all experiments so far have been performed on lateral and vertical devices from the III-V semiconductor material system. Here the addition of magnetic dopants also alters the electronic properties of the system and impedes the fabrication of artificial atoms with a strong magnetic response. Whereas in the II-VI semiconductor material system the incorporation of magnetic ions is isoelectric and thus leaves the electronic properties of the material unaffected. Furthermore it is well known from the intense study and characterization of these diluted magnetic semiconductors, that they exhibit a strong magnetic response, the Giant-Zeeman splitting [Gaj 79, Twar 84, Furd 88]. Based on the work of Slobodskyy et al. [Slob 03], Gould et al. [Goul 06] and Rüth et al. [Ruth 11b] it has been shown that this material can be implemented in electronic devices such as RTDs. On the one hand the strong magnetic response of the material is preserved, on the other hand novel physical properties can be observed, i.e. zero-field splitting of the QW's energetic levels. Therefore the use of the II-VI DMS material system for the fabrication of artificial atoms opens a way to a new field of exciting opportunities for electric and magnetic tunability at once. The first attempt to fabricate gated II-VI submicron RTD devices [Borz 07], however proved to be more challenging than in the III-V semiconductor material system.

In this work the development, the final process for the fabrication and the observation of artificial magnetic atoms from the DMS (Zn,Cd,Be,Mn)Se are presented. The thesis is

organized as follows. The first part of chapter 2 presents the basic physics and electronic transport properties of quantum dot devices of circular symmetry, which form the artificial atoms. In the second part the II-VI heterostructure from (Zn,Cd,Be,Mn)Se is introduced and the magnetic properties of the magnetically doped (Zn,Mn)Se QW are reviewed. It also includes a general look on the implications arising from combining the single-particle energy spectrum with the Giant-Zeeman energy splitting. The last section describes the tunning of the QW in order to bring its lowest energy level as close as possible to the Fermi energy in the leads. This is necessary for performing experiments in the linear transport regime.

Chapter 3 addresses the development of a proper contacting scheme in the submicron devices. Due to the pseudomorphic growth of the II-VI heterostructure on a GaAs wafer, a contact on the wafer backside cannot be used. Instead a continuous highly doped layer below the DBH is used to contact the backside of the device. But in order to avoid parasitic currents a clear current path through the device has to be ensured. Therefore the backside layer and the II-VI superlattice buffer, screening the RTD heterostructure from the III-V/II-VI interface electric fields, have to be cut through. Here the development of a reliable fabrication process for  $\geq 1.3~\mu m$  separating trenches is presented.

The second part of the chapter presents methods for contacting the top of the submicron pillars. Therefore the idea of metal capped, insulating semiconductor line mesas [Aust 96] is tested for the II-VI heterostructure. However the method proves to be not applicable to our material system and thus the air-bridge technique [Borz 04] is adjusted to the profile of the device.

In the following the miniaturization of the RTD pillars to submicron dimensions and is presented in chapter 4. Here the challenges in the fabrication process are discussed and the necessary solutions are outlined. The different development steps are accompanied by electronic and magnetic transport measurements. These ensures that the electronic and magnetic properties of the RTD heterostructure are unimpaired.

Having established a fabrication process for vQDots from submicron pillars in the II-VI RTD, the addition of the gate electrode is outlined in chapter 5. The requirement of a dielectric material is discussed and subsequently the characterization of the available dielectrics:  $SiO_2$  and  $Si_3N_4$  is presented. Therefore the challenges arising from the current RTD heterostructure are considered in the design as well as the fabrication of the gate electrode in order to ensure maximum functionality. The suitability of the fabrication and its impact on the device functionality is monitored by electrical measurements.

With all fabrication steps established, chapter 6 summarizes the entire process to fabricate artificial magnetic atoms from the II-VI DMS. The basic fabrication method is complemented with a further developed process, which is more universally valid and does not take advantage of any special properties of the used wafer or dielectric material. The second part of this chapter then presents the observation on vQDots from the (Zn,Cd,Be,Mn)Se RTD heterostructure. It discusses the first observations of the formation of an artificial magnetic atom considering the electronic and magnetic device properties.

12 1. Introduction

# Chapter 2

# State of the art quantum dots and diluted magnetic semiconductors

At the time this thesis has been started, a demonstration of artificial magnetic atoms has not yet been done. The study of non-magnetic artificial atoms however was a rather mature field. Indeed already in the 1990's the formation of semiconductor quantum dots in lateral and vertical configuration has been extensively investigated and a parallel to observations made in real atoms has been pointed out [Asho 96, Kouw 97]. The relevant physical characteristics of these artificial atoms from quantum dots are examined in the first section of this chapter. Since the fabrication of artificial atoms from a magnetic semiconductor is the scope of this work, the used II-VI material system from (Zn,Cd,Be,Mn)Se is presented subsequently. It is also shown, how the magnetic properties resulting from adding Mn into the II-VI semiconductor are expected to modify the quantum dot's magnetic response. In the last part of the chapter the enhancements to the state of the art double barrier heterostructure developed by Slobodskyy et al. [Slob 03] are presented together with the results from electronic transport measurements. These results lead to a II-VI RTD heterostructure suitable to perform the necessary electronic transport on quantum dots in the linear regime.

## 2.1 Artificial atoms from quantum dots

This section presents a brief overview on the physics and electronic transport through semiconductor quantum dots, as artificial atoms, relevant to this work. The reviews on artificial atoms and few-electron quantum dots of Ashoori [Asho 96], Kouwenhoven *et al.* [Kouw 97, Kouw 01], Reimann *et al.* [Reim 02] and Hanson *et al.* [Hans 07] as well as the PhD thesis of T. H. Oosterkamp [Oost 99] serve as a basis.

Quantum dots from semiconductors, forming 0D objects, are structures of a few 100 nm in size holding a number 1 to 1000 free electrons. For electronic transport these small boxes are coupled via tunnel barriers to the reservoirs in the leads. The electrostatic potential of a quantum dot can be altered relative to the reservoirs by adding one or more gate electrodes to the system. With that said changing the gate voltage allows to

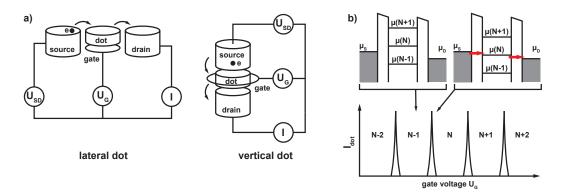

Fig. 2.1: a) Schematic quantum dot design of lateral and vertical configuration. The quantum dot is depicted by a circular disc with gapped connections (representing the tunnel barriers) to source and drain reservoirs. Creating a closed-circuit the current I through the device is measured with respect to a bias voltage  $U_{SD}$  and a gate voltage  $U_{G}$ . b) Schematic illustration of the Coulomb blockade in the case of low bias regime. (Left) No electrochemical potential of the dot is located within the bias window, thus no current flows through the device. (Right) The  $\mu(N)$  level is situated inside the bias window, allowing electrons to pass from the source to the drain and enabling a current flow. (Bottom) The resulting current  $I_{dot}$  versus  $U_{G}$ . [Kouw 97, Hans 07]

precisely vary the number of electrons within this box. Attaching voltage and current probes to this three terminal device, the electronic properties are investigated (fig.2.1a.)

The observed electronic properties of these quantum dots are similar to the discrete energy spectrum in real atoms but dominated by mainly two effects: the Coulomb repulsion of the electrons on the dot and the discrete energy spectrum arising from the confinement in all three directions. These electronic properties are described to first approximation by the constant interaction model, which is based on two assumptions. First, the interaction of the electrons inside the dot with the electrons of the environment is parametrized by a constant capacitance C,

$$C = C_S + C_D + C_G \tag{2.1}$$

where  $C_S$ ,  $C_D$  and  $C_G$  stand for the capacitance of the dot to the source, drain and gate, respectively. Second, the single-particle energy-level spectrum of the 0D object is assumed to be independent of these Coulomb interactions and not affected by the number of electrons in the dot. The total energy of an N electron dot is thus approximated by

$$U(N) = \frac{(-e(N - N_0) + C_G V_G)^2}{2C} + \sum_{n=1}^{N} E_{n,l}(B)$$

(2.2)

where e is the electron charge,  $N_0$  stands for the number of electrons on the dot at  $V_G = 0$  V, the continuously alterable charge  $C_G V_G$  denotes the charge that is induced on the dot by  $V_G$  and the last term is a sum over the occupied single-particle energy levels  $E_{n,l}(B)$ . Only the later are dependent on the applied magnetic field and are given by the confining potential of the quantum dot.

The electrochemical potential  $\mu(N)$ , representing the transition between the N-electron ground state and the (N-1)-electron ground state, is defined as

$$\mu(N) \equiv U(N) - U(N-1)$$

$$= \left(N - N_0 - \frac{1}{2}\right) E_C - e \frac{C_G}{C} V_G + E(N)$$

(2.3)

with  $E_C = e^2/C$  the charging energy and  $E_N$  the topmost filled single-particle energy level of the N-electron dot. The spacing of adjacent electrochemical potentials is then given by the addition energy

$$E_{add}(N) \equiv \Delta \mu(N) = \mu(N+1) - \mu(N) = E_C + E_{N+1} - E_N = E_C + \Delta E$$

(2.4)

consisting solely of the charging energy  $E_C$  and the spacing  $\Delta E$  among two consecutive discrete energy levels  $E_{N+1}$  and  $E_N$ .

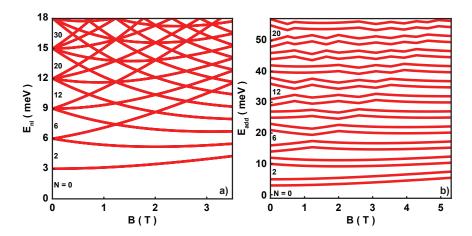

As previously reported, the energy levels  $E_{n,l}$  form the single-particle energy spectrum which arises from the confinement potential of the dot. By fabricating devices of different shapes, i.e. triangle, square, etc., one can only introduce asymmetries in the lateral confinement deforming a rotationally symmetric harmonic potential [Taru 97]. These induced asymmetries mainly lift degeneracies originating from a highly symmetric confinement potential. Thus the circular shape, having however the highest degree of symmetry and having been extensively investigated in the past, is also selected for the pillars in this work. Within a pillar of a circular design the vertical quantum dot has then the shape of a 2D disc formed from the circular quantum well between the barriers. The resulting confinement potential of the disc can be approximated by a 2D harmonic potential  $V(r) = \frac{1}{2}m^*\omega_0^2r^2$ , where  $\omega_0$  is the oscillator frequency. The Schrödinger equation for this 2D harmonic potential in the presence of a magnetic field B can be solved analytically and leads to the Fock-Darwin spectrum [Fock 28, Darw 30]

$$E_{n,l} = (2n + |l| + 1)\hbar\sqrt{\frac{1}{4}\omega_c^2 + \omega_0^2} - \frac{1}{2}l\hbar\omega_c$$

(2.5)

where  $\hbar\omega_0$  denotes the electrostatic confinement potential,  $\hbar\omega_c = \hbar eB/m^*$  is the cyclotron energy,  $m^*$  stands for the effective electron mass and the radial and angular quantum numbers are n and l. For B=0 T the high degree of symmetry in the circular design leads to sets of energetically degenerate single-particle levels. The emerging shell structure with the 'magic' numbers 2, 6, 12,... [Kouw 01], see figure 2.2, resembles the one of real atoms with completely filled shells at the atomic numbers 2, 10, 18,... These physical characteristics of a quantum dot, which are akin to the ones in real atoms, has lead to the term 'artificial atom'.

It should further be mentioned that each energy level  $E_{n,l}$  is two-fold spin-degenerate. The alignment of the spins with the external field can however be accounted for by the

Fig. 2.2: a) Calculated Fock-Darwin spectrum of a parabolic potential with  $\hbar\omega_0 = 3$  meV in a GaAs quantum dot, describing the evolution of single-particle states  $E_{n,l}$  in a magnetic field. Each state is two-fold spin-degenerate, due to Zeeman energy neglection. b) The addition energy  $E_{add}$  of this system is given by equation 2.4 and using a fixed charging energy  $E_C = 2$  meV.

Zeeman spin-splitting  $\Delta E_Z = g\mu_B B$ , where g is the Landé-factor and  $\mu_B$  the Bohr magneton. In the III-V material system the g-factor is small ( $g_{GaAs} = -0.44$ ), so  $E_Z$  ( $E_Z(GaAs) = 25 \mu eV$ ) is much smaller than the other energy splittings in a quantum dot and thus usually neglected, leaving each single-particle energy level two-fold degenerate.

More thorough investigations of the evolution of the energy levels in an increasing magnetic field revealed a spin-polarized filling of the shells at B=0 T [Taru 96]. In other words degenerate states are, as much as possible, first filled by electrons with parallel spins up to the point where the shell is half filled, which corresponds in fact Hund's first rule in atomic physics. In the energy spectrum of a quantum dot this becomes apparent by enhancements for i.e. N=9, corresponding to a spin-polarized, half-filled third shell. This fact once more emphasizes the analogy between the physical properties of the 0D object formed in a quantum dot and real atoms.

When performing measurements on a quantum dot there are three temperature regimes to be distinguished:

- (1)  $e^2/C \ll k_B T$ , the high temperature limit, where the discrete charging cannot be discerned,

- (2)  $\Delta E \ll k_B T \ll e^2/C$ , the classic Coulomb blockade regime, where discrete charging is observable, but many single-particle energy levels are excited by thermal fluctuations,

- (3)  $k_BT \ll \Delta E \wedge k_BT \ll e^2/C$ , the quantum Coulomb blockade regime, where discrete charging and single-particle energy levels are examinable.

For performing transport spectroscopy on a quantum dot's energy spectrum the third regime is required. In order to observe effects due to discrete charging a second criterion has to be met by any device. Based on the typical time to charge and discharge the quantum dot  $\Delta t = R_t C$  and the Heisenberg uncertainty  $\Delta E \Delta t > h$  the tunnel resistance  $R_t$  has a lower limit of

$$R_t \gg e^2/h \tag{2.6}$$

which is called the weak coupling regime. For the vertical quantum dots used in this thesis this criterion is met.

Transport in gated transport spectroscopy occurs when the electrochemical potential of the dot  $\mu(N)$  aligns with those of the source  $\mu_S$  and drain  $\mu_D$ . A source drain voltage  $V_{SD} = (\mu_S - \mu_D)/(-e)$  opens a bias window, allowing electrons to tunnel from one reservoir to the other when  $\mu(N)$  is located in it, meaning  $\mu_S \geq \mu(N) \geq \mu_D$  for at least one value of N. If this condition is not satisfied, then no current flows through the dot and the number of electrons therein remains unchanged. This is known as Coulomb blockade. Varying  $V_G$ ,  $\mu(N)$  can be realigned with the bias window lifting the Coulomb blockade and enabling electron tunneling from source to drain. In the low-bias regime only one dot level is within the bias window and sweeping  $V_G$  generates a current trace  $I_{Dot}$  as schematically depicted in figure 2.1b. In contrast when the bias window is chosen such that multiple dot levels are situated therein the measurement takes place in the high-bias regime.

## 2.2 The II-VI material system

### 2.2.1 (Zn,Be,Cd,Mn)Se semiconductor alloy

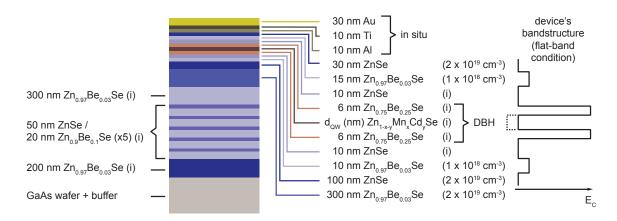

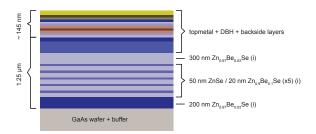

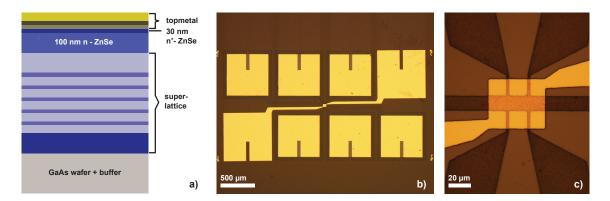

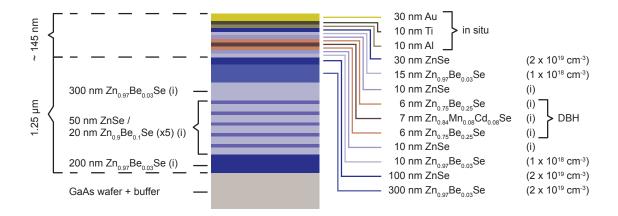

The development, fabrication and investigation of vertical quantum dots performed during this thesis are done on multilayer heterostructures from the II-VI semiconductor material system (Zn,Be,Cd,Mn)Se. The sequence of layers in the heterostructure, which is depicted in figure 2.3 and described in detail later in this section, results in the formation of a II-VI resonant tunneling diode (RTD) [Chan 74]. The thin and abrupt tunnel barriers in such a heterostructure, which are weakly affected by a gating potential, provide already a well defined confinement along the growth direction (usually referred to as the z-direction). Furthermore the wide-gap II-VI semiconductor ZnSe ( $E_g(4.2 \text{ K}) = 2.82 \text{ eV}$  [Land 99]) acts as the base semiconductor for the entire heterostructure. In contrast to the III-V material system, used previously to fabricate vertical quantum dots, the incorporation of Mn atoms for inducing magnetic properties does not alter the doping of the material. In fact the detached electric and magnetic properties in the II-VI material system, which will be discussed later, allow tunability of doping and band structure useful for device optimization as well as investigation of spin related phenomena.

The ZnSe based multilayer heterostructures are typically grown on GaAs substrates, because there is only a small lattice mismatch of 0.27 % [Land 99] and they are readily available. Adding Be to ZnSe layers and creating the ternary alloy  $\text{Zn}_x\text{Be}_{1-x}\text{Se}$  two effects can be achieved. First, its incorporation decreases the lattice constant of the layer, due to the smaller lattice constant of BeSe [Land 99]. This fact allows to reduce the elastic strain enabling a pseudomorphic growth of the device's heterostructure. Second, the tunability of the band gap [Asta 02, Chau 00], which comes from Be incorporation,

**Fig. 2.3:** The entire II-VI heterostructure layout built up from: the GaAs wafer, the superlattice, the RTD device and *in situ* metalization. (Right) Schematic, the RTD device bandstructure (in flat-band condition) indicating the band gap reduction when Cd is incorporated.

makes it a perfect fit for creating the tunnel barriers necessary for the resonant tunneling diode. This aspect also benefits from the fact that the increase in band gap energy at the type I heterointerface  $\text{ZnSe}/\text{Zn}_x\text{Be}_{1-x}\text{Se}$  occurs predominantly in the conduction band [Kim 00, Koen 99]. The quantum well of the resonant tunneling device is formed from the diluted magnetic semiconductor  $\text{Zn}_x\text{Mn}_{1-x}\text{Se}$ . Based on the results of Slobodskyy et al. [Slob 03] the Mn concentration is 8 % in all devices of this thesis. Quantum well II-VI RTD heterostructures grown by Slobodskyy et al. [Slob 03] and Frey et al. [Frey 10b] exhibit resonances above  $U_{SD}=100$  mV. In order to align the resonance with the Fermi energy in the leads, small amounts (up to 8 %) of Cd are alloyed into the QW. Since pure CdSe has a band gap of  $E_g=1.74$  eV [Lunz 96], which is smaller than  $E_g(\text{ZnSe})$ , Cd is an adequate candidate for fine tunning the band gap of the quantum well. Finally the electric conductivity through the device is achieved by appropriately n-doping the contact layers and the semiconductor leads to the DBH with iodine [Shib 88].

Figure 2.3 presents the entire II-VI heterostructure which was grown by Frey [Frey 12] using molecular beam epitaxy (MBE). This heterostructure, which consists of two main blocks, is grown on a standard epi-ready GaAs wafer, followed by a 180 nm undoped GaAs buffer layer. The first block of the heterostructure consists of a 200 nm thick highly doped ZnSe screening layer, followed by 7 periods of an undoped ZnSe /  $\rm Zn_{0.9}Be_{0.1}Se$  (50 nm / 20 nm) superlattice and a 300 nm thick undoped  $\rm Zn_{0.97}Be_{0.03}Se$  layer. This way the influence of electrical fields and charging from the polar III-V/II-VI interface[Frey 09, Farr 91, Frey 10a] is eliminated (see also chapter 3.1).

The second block represents the RTD heterostructure itself, which is based on the research done by Slobodskyy *et al.* [Slob 03]. Except for small variations in barrier width and height as well as QW composition and width, which required to be adjusted due to variation in growth conditions, the layer properties remained unchanged. Following the MBE growth, the first two layers of this block form the backside contact. The first one consists of a 300 nm thick  $Zn_{0.97}Be_{0.03}Se$  (2 × 10<sup>19</sup> cm<sup>-3</sup>) doped layer and is matched to GaAs, preventing the addition of strain to the structure. The second layer of the two is a

100 nm thick ZnSe (2 × 10<sup>19</sup> cm<sup>-3</sup>) doped layer to minimize contact resistance [Miya 92]. 10 nm Zn<sub>0.97</sub>Be<sub>0.03</sub>Se (1 × 10<sup>18</sup> cm<sup>-3</sup>) and 10 nm undoped ZnSe act as the source to the following DBH. The later is formed from 6 nm thick barriers of Zn<sub>0.75</sub>Be<sub>0.25</sub>Se and a QW from Zn<sub>1-x-y</sub>Cd<sub>y</sub>Mn<sub>x</sub>Se of different widths  $d_{QW}$ . Drain and top contact are then provided by 10 nm undoped ZnSe followed by 15 nm Zn<sub>0.97</sub>Be<sub>0.03</sub>Se (1 × 10<sup>18</sup> cm<sup>-3</sup>) and 30 nm ZnSe (2 × 10<sup>19</sup> cm<sup>-3</sup>). The heterostructure is completed by in situ metal evaporation of Al / Ti / Au (10 nm / 10 nm / 30 nm), again to minimize contact resistance[Maxi 04].

### 2.2.2 Diluted magnetic semiconductor (Zn,Mn)Se

Diluted magnetic semiconductor stands for a semiconducting alloy formed from randomly substituting some of the host crystal's cations by magnetic ions, in this case  $Mn^{2+}$ . Unlike in (Ga,Mn)As, where  $Mn^{2+}$  is p-doping the III-V semiconductor through adding acceptor states, in II-VI semiconductors the isoelectric incorporation of the  $Mn^{2+}$ -ion does not change the crystal's electric properties. When Mn is built into the II-VI semiconductor crystal, i.e. the zincblende crystal of ZnSe, its two 4s electrons participate in the formation of the crystal bonds. The five d electrons of the half filled 3d orbitals are however localized and their spins are aligned in parallel, according to Hunds rules. The total spin  $S_{Mn}$  of the manganese atom is thus 5/2. These randomly distributed magnetic ions in the semiconductor crystal induce strong Zeeman splittings of electronic levels in an external magnetic field. This originates in an exchange interaction between the s/p band electrons, referring to the conduction/valence band respectively, and the d electrons from the  $Mn^{2+}$ ions [Furd 87, Furd 88].

The magnetization M of the paramagnetic phase of a  $A_{1-x}^{II}Mn_xB^{VI}$  DMS in the very dilute limit (x < 0.01) can approximately be expressed by the formula

$$M = xN_0g\mu_BSB_S(g\mu_BSH/(k_BT))$$

(2.7)

where x is the magnetic ion mole fraction,  $N_0$  is the number of cations per unite volume, H represents the applied field,  $B_S$  is the standard Brillouin function, g stands for the electron g-factor, T denotes the temperature and S is the manganese spin. For arbitrary values of x and T however the analytical expression from above is no longer valid. Gaj et al. [Gaj 79] observed a similar qualitative correlation of the magnetisation M vs. H and the Brillouin function. This purely empirical finding replaces x and T by effective values  $x_{eff}$  and  $T_{eff} = T - T_0$  in the magnetisation M

$$M = x_{eff} N_0 g \mu_B S B_S \left( \frac{g \mu_B S H}{(k_B (T - T_0))} \right)$$

(2.8)

where  $x_{eff}$  and  $T_0$  are fitting parameters and can be tabulated for each family of DMS. The reduced mole fraction of active  $Mn^{2+}$ -ions, accounted for by  $x_{eff}$ , is based on the  $Mn^{2+}$ - $Mn^{2+}$  antiferromagnetic interaction of a small fraction of ions which form clusters with a zero net magnetic moment [Shap 84]. Hence, the energy of up or down electron spin levels in the conduction band, based on the s-d-interaction, is given by [Gaj 79, Twar 83, Twar 84]

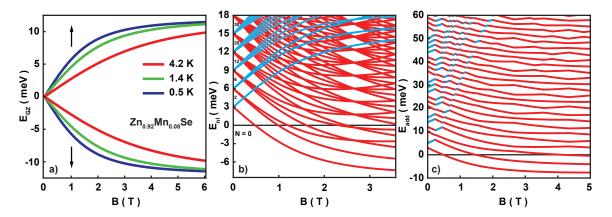

Fig. 2.4: a) Giant Zeeman energy of the electronic spin-up and spin-down levels in a  $\text{Zn}_{0.92}\text{Mn}_{0.08}\text{Se}$  layer at different temperatures. b) Calculated Fock-Darwin spectrum from figure 2.2 for a  $\text{Zn}_{0.92}\text{Mn}_{0.08}\text{Se}$  quantum dot supplemented with the Giant Zeeman splitting between spin-up (blue) and spin-down (red) electrons. c) The addition energy  $E_{add}$  of this system, given by equation 2.4, using a fixed charging energy  $E_C = 2$  meV.

$$E_{GZ\uparrow,\downarrow} = \pm \frac{1}{2} N_0 \alpha x S_{eff} B_S \left( \frac{g\mu_B SH}{(k_B (T - T_0))} \right)$$

(2.9)

and the total energy splitting reads

$$\Delta E_{GZ} = N_0 \alpha x S_{eff} B_S \left( \frac{g \mu_B S H}{(k_B (T - T_0))} \right)$$

(2.10)

where  $N_0\alpha$  is the material dependent exchange integral for the s-d-interaction and  $S_{eff}$  (with  $S_{eff} < S_{Mn}$ ) stands for an effective spin at a given manganese concentration x alloyed with the semiconductor. For (Zn,Mn)Se Twardowski et al. [Twar 83, Twar 84] determined  $N_0\alpha = 0.26$  eV. Keller [Kell 04] measured  $S_{eff} = 1.13$  and  $T_0 = 2.35$  K for a manganese concentration of 8%, similar to the concentration used in the QWs of the samples processed in this thesis. Figure 2.4a displays a calculated spin-splitting of the conduction band edge at different temperatures for Zn<sub>0.92</sub>Mn<sub>0.08</sub>Se from the formula and values for  $N_0\alpha$ ,  $S_{eff}$  and  $T_0$  mentioned above.

As mentioned in section 2.1, for the QDots made out of a III-V semiconductor the consideration of Zeeman spin-splitting within the Fock-Darwin spectrum is neglected. This however is no longer valid for the Giant Zeeman splitting in a II-VI DMS, where the energetic splitting is equal or higher than the energy spacing from a 3D confinement. The Fock-Darwin single-particle energy spectrum of a DMS QDot is then given by

$$E_{n,l,\uparrow,\downarrow} = (2n + |l| + 1)\hbar\sqrt{\frac{1}{4}\omega_c^2 + \omega_0^2} - \frac{1}{2}l\hbar\omega_c \pm \frac{1}{2}N_0\alpha x S_{eff}B_S\left(\frac{g\mu_B SH}{(k_B(T - T_0))}\right)$$

(2.11)

where the first and second term are the spin independent single-particle energy spectrum and the third term introduces the Giant-Zeeman spin splitting. Figure 2.4b displays how

the spin-independent Fock-Darwin spectrum, previously shown in figure 2.2, is affected by the spin splitting in a magnetic artificial atom, when a magnetic field is applied. The measureable addition energy of the magnetic QDot is depicted in figure 2.4c, when a charging energy of  $E_c = 2$  meV is added to each level of  $E_{n,l}$ .

## 2.3 Quantum well energy adjustment

The investigation of electronic and magnetic properties of vQDots is best performed in the linear transport regime. This means the current through the sample is determined while a small source-drain voltage  $U_{SD}$  is applied. In order to do so it is necessary that the QDot's energy levels are as close as possible to the Fermi energy of the leads. This way by applying a gate voltage these levels, which are typically separated by a few meV, can easily be located inside a small bias window.

These QDot energy levels originate from confining the electron wave in the x, y and z spacial direction. The z-confinement is given by the QW's thickness of a few nm and results in energetic spacings  $\Delta E_z$  from many tens of meV to over hundred. However, the 2D confinement in x-y-direction arises from the lateral miniaturization when etching the pillar to form the vQDot. Thereby the  $E_{xy}$ -degeneracy of each QW's  $E_z$  energy state is lifted. Due to the pillar's lateral dimensions of a few-hundred nm the energetic spacings  $\Delta E_{xy}$  result in gaps of some meV. Since only a small fraction of the QW's total energy spectrum is accessible by the gate voltage, the electronic investigations are concentrating on the  $E_{xy}$  quantization for a fixed  $E_z$ . Therefore, the mentioned requirement for linear transport is achieved when a  $E_z$  energy level of the two dimensional QW, preferably the QW's ground state, is already situated near the Fermi level of the contacts. This requirement however is not met at the starting point of the development of vQDots from the II-VI semiconductor RTD-structure.

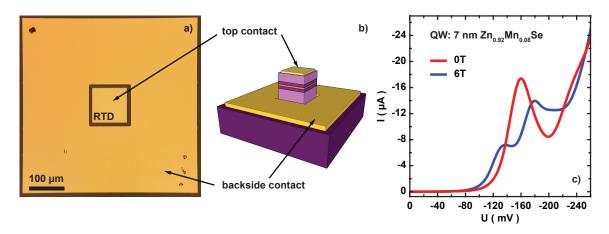

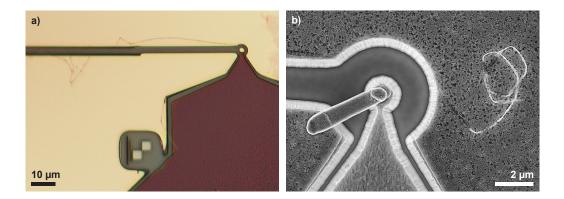

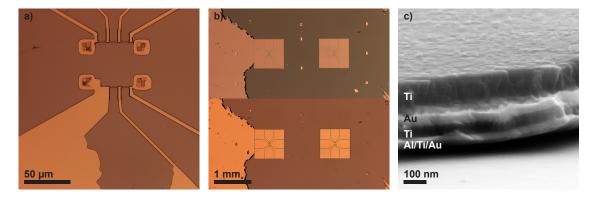

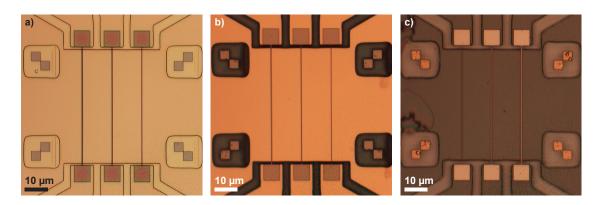

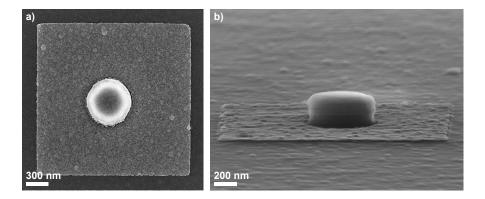

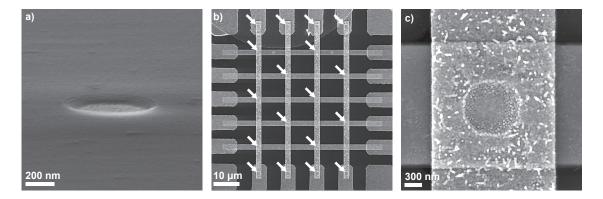

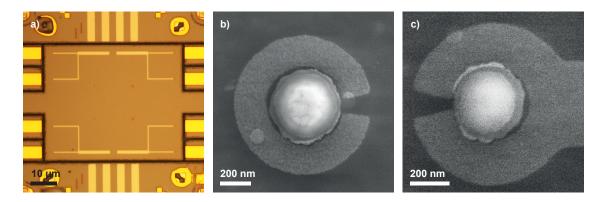

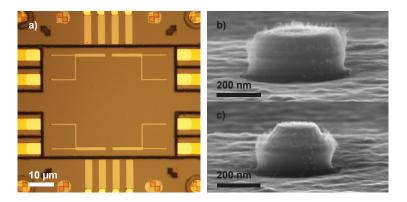

**Fig. 2.5:** a) Optical image of a  $100^2~\mu\text{m}^2$  QW RTD device used for characterization. b) Schematic side view of the QW RTD device. c) I-U curves at B=0 T and 6 T from a  $100^2~\mu\text{m}^2$  RTD device with a 7 nm  $\text{Zn}_{0.92}\text{Mn}_{0.08}\text{Se}$  quantum well showing the Giant-Zeeman splitting of the resonance.

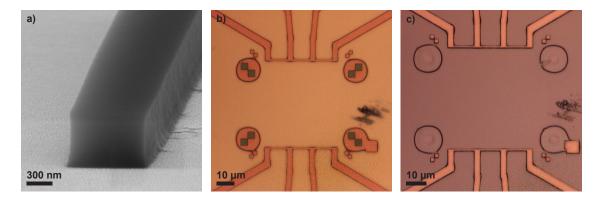

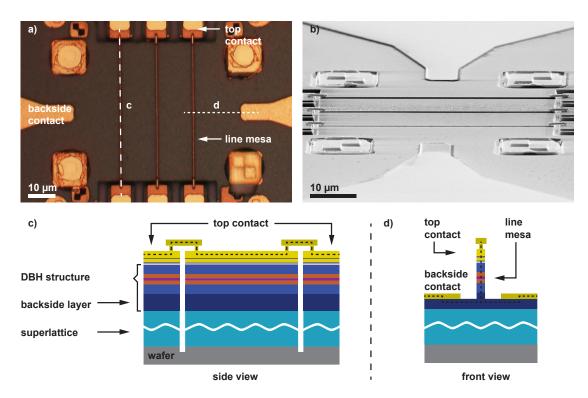

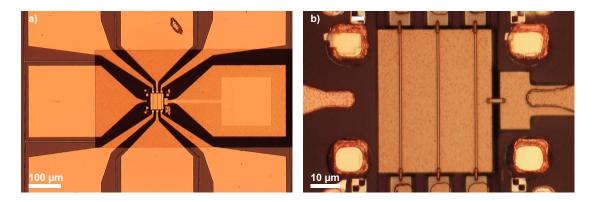

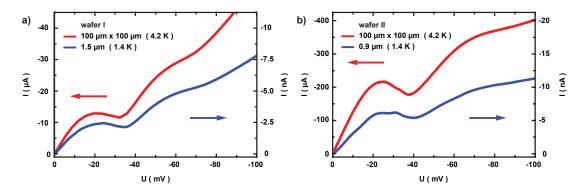

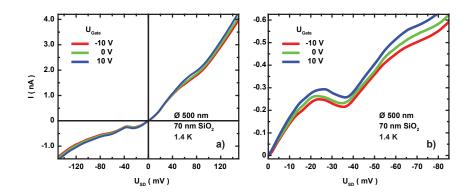

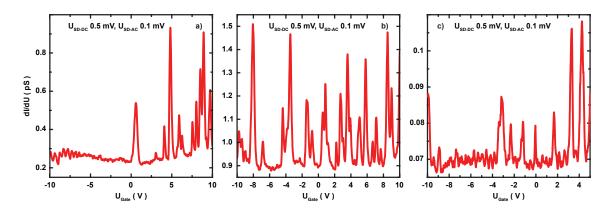

As mentioned earlier the entire RTD-device is based on the heterostructure developed by Slobodskyy et al. [Slob 03] combined with the insulating superlattice described by Frey et al. [Frey 09]. However, the MBE growth necessary for all the samples presented in this work is performed by A. Frey and described in detail in his PhD thesis [Frey 12]. Also a detailed model of the electronic transport in the RTDs QW from the II-VI DMS is presented in the PhD thesis of Rüth [Ruth 11a]. At the starting point [Frey 10b], the RTD's DBH is typically formed from 6 nm Zn<sub>0.75</sub>Be<sub>0.25</sub>Se / 7 nm Zn<sub>0.92</sub>Mn<sub>0.08</sub>Se / 6 nm Zn<sub>0.75</sub>Be<sub>0.25</sub>Se. The grown heterostructures are electrically characterized by first fabricating  $100^2 \mu m^2$ ,  $120^2 \mu m^2$ ,  $150^2 \mu m^2$  square pillars through optical lithography, Ti/Au/Ti metal mask evaporation and chemical assisted ion beam etching (CAIBE) down to the backside layer. Each pillar is surrounded by a  $500^2~\mu\mathrm{m}^2$  square shaped backside contact-ring, fabricated by optical lithography, electron beam evaporation of Ti/Au and lift-off. Figure 2.5a shows a top view of a  $100^2 \mu m^2$  characterization RTD-device and a sketched side view is displayed by figure 2.5b. Figure 2.5c shows characteristic 2-terminal I-U-curves of a  $100^2 \ \mu\text{m}^2$  device at B = 0 T and 6 T. The voltage  $U_{res} = (-161 \pm 1) \text{ mV}$ indicates at which source drain voltage the first QW-level is in resonance with the Fermi energy in the top contact. This value lies within the range of -155 mV to -165 mV, given by the growth to growth variations. A similar observation is true for the peak-to-valleyratio (PVR) of 1.92, which is in this case at the top end of the 1 to 2.2 range in the II-VI RTDs. From the position of the LO-phonon resonance [Gold 87] at  $U_{LO} = (-232 \pm 1) \text{ mV}$ and the known LO-phonon energy in ZnSe  $E_{LO} = 31.7$  meV [Land 99] the lever factor, which connects the difference in voltage to the energetic spacing, is found to be  $\lambda = (2.24)$  $\pm$  0.06) mV/meV. The spacing of the two resonances at  $U_{res,1}=(-137\pm1)$  mV and  $U_{res,2} = (-180 \pm 1) \text{ mV}$  in the 6 T curve gives a Giant-Zeeman energetic spacing of the spin-up and spin-down level in the QW of  $\Delta E_{GZ} = (19 \pm 2)$  meV, taking into account the aforementioned lever factor  $\lambda$ . This corresponds well with the expected energetic splitting of  $\Delta E_{GZ} = 19.6$  meV, given by the empirical equation 2.10. The described behavior is typical for the grown RTDs with a Zn<sub>0.92</sub>Mn<sub>0.08</sub>Se and confirms that the expected QW's magnetic properties are preserved.

However the first resonance, denoted by the voltage position of the resonance peak, of these QW RTDs is well above the Fermi energy in the leads. It is broader than expected from tunneling theory, because of QW width fluctuation as described by the model of Rüth [Ruth 11a]. Furthermore, the read-out  $U_{res}$ -values from the I-U-curves agree well with the determined positions of the maxima of the second derivative  $dI^2/dU^2$ , as proposed by Smith  $et\ al.$  [Smit 96] and Yoh  $et\ al.$  [Yoh 98]. The later is helpful, when extremely broad resonant peaks, i.e. the LO-phonon peak, are investigated. Finally is has to be pointed out that there is an observable asymmetry between the voltages at which the resonances are observed in positive and negative source drain bias (not explicitly shown here). The reason for the difference may well be in growth related issues as there are the segregation of alloys at interfaces of different layers and small variations in the layers surrounding the DBH [Frey 12]. With these facts established this QW DBH has to be modified such, that the Fermi level of the QW aligns with the Fermi energy in the leads, allowing to perform measurements in the linear response regime. For this purpose two

possibilities for lowering the energy level present: increasing of the QW width or forming a QW from an alloy with a smaller band gap. The investigation of this options, which led to the optimal QW for the magnetic QDots, is presented in the following.

#### 2.3.1 Width variation

In order to investigate how changes in the DBH's conduction band profile, presented in figure 2.6a, affect its electronic properties, one has to look into how these changes are connected to the physical properties. Neglecting any contributions from the contacts and just considering a DBH plus its adjacent leads the passing current is given by the formula

$$J \propto \int T(E)D_S(E)D_D(E+eU)(f_S(E)-f_D(E+eU))dE \qquad (2.12)$$

where  $D_S(E)$  and  $D_D(E + eU)$  are the density of states and  $f_S(E)$  and  $f_D(E + eU)$  denote the Fermi distributions in the source and drain, accounting for an applied bias voltage U. T(E) is the transmission probability through the DBH and is given by the physical characteristics of the DBH. Using the transfer matrix method as described in [Mizu 95, Leps 97] the transmission probability T(E) can be expressed

$$T(E) = \frac{m_D^* k_D}{m_S^* k_S} \frac{1}{|M_{11}^{tot}|^2}$$

(2.13)

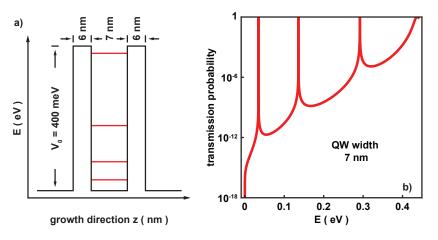

where  $m_D^*$  and  $m_S^*$  are the effective masses and  $k_D$  and  $k_S$  are the electron wavenumbers in the source and drain.  $M_{11}^{tot}$  is the (11)-element of the total transfer matrix formed from the transfer matrices at each DBH's interface. Figure 2.6b presents qualitatively the T(E) for a flat band DBH with a barrier height of 400 eV from  $\text{Zn}_{0.75}\text{Be}_{0.25}\text{Se}$  and

**Fig. 2.6:** a) Schematic of the conduction band profile in growth direction under flat-band condition. Two 6 nm thick  $Zn_{0.75}Be_{0.25}Se$  layers forming the tunnel barriers confine a 7 nm thick  $Zn_{0.92}Mn_{0.08}Se$  quantum well. b) The arising discrete energy states inside the quantum well result in peaks of unity in the calculated transmission probability as a function of the incident electron energy.

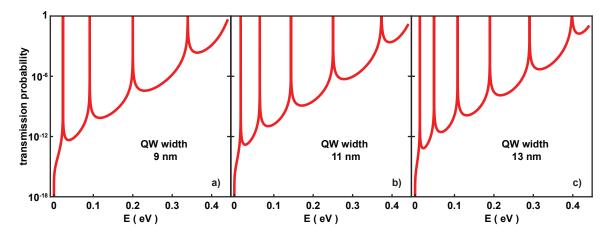

**Fig. 2.7:** Calculated transmission probability for the double barrier heterostructure in figure 2.6 with varying quantum well thicknesses of a) 9 nm, b) 11 nm and c) 13 nm showing the decrease of the energetic position of the first resonance towards lower energies as the quantum well thickness is increased.

6 nm thickness as well as a 7 nm wide ZnSe QW. Moreover, for all segments of the energy potential a constant effective mass  $m^* = 0.145 \ m_e$  is assumed. The difference between the aforementioned resonance  $U_{res}$  and the one of the simulation is based on the simplicity of the model which lacks further device parameters. A detailed treatment on this problem is presented by [Ruth 11a] and is beyond the scope of this thesis.

A first strategy to approach the resonance to the Fermi energy of the contacts, meaning to move  $U_{res}$  towards 0 V, consists in varying the width of the QW. As it is observable from the transmission probability T(E) for QWs of 9 nm, 11 nm and 13 nm, depicted in figure 2.7, the first resonance is shifting towards lower energies. This means the QW's ground energy is lowered towards the conduction band edge and with all other parameters remaining unchanged its distance to the Fermi level is reduced. This simple picture suggests a valid possibility to achieve the intended linear transport regime in the RTD device.

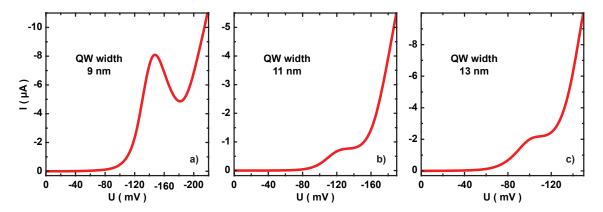

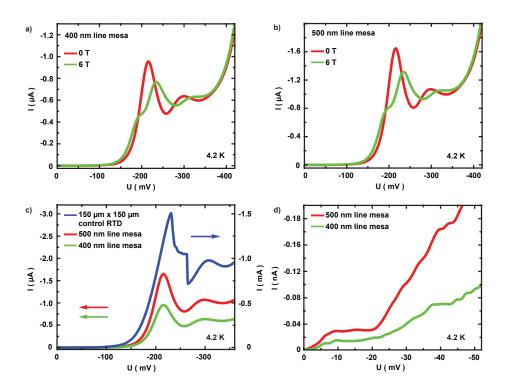

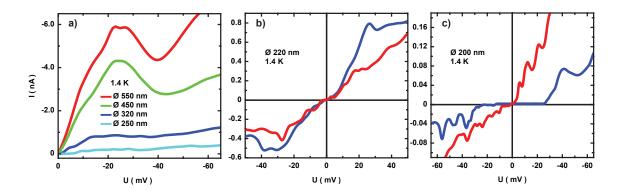

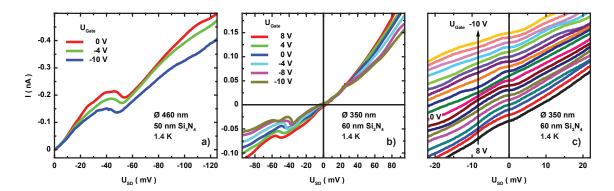

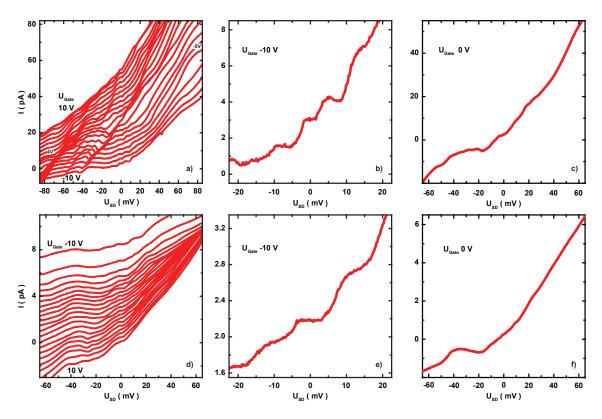

Figure 2.8 presents I-U measurements from standard  $100^2 \ \mu m^2$  RTD devices where the QW are 9 nm, 11 nm and 13 nm. As expected the resonance moves to lower bias voltages as a function of the QW width and goes down as far as  $U_{res} = 100 \ \text{mV}$  for a 13 nm QW. This shift is accompanied by a broadening of the resonance as well as a drop of the PVR down to 1, reducing the observation of a clear resonance peak. Additionally, since the decrease in  $U_{res}$  by doubling the QW width does not shift the resonance significantly near zero bias voltage, this path proves to be not suitable for the intended objective and is not further pursued.

## 2.3.2 Bandgap variation

The second possible approach is based on reducing the energy gap of the semiconductor alloy in the QW. By this means, the conduction band bottom is lowered and therefore all

energy levels of the QW are also shifted to lower energies. With that said this method offers the possibility to align the ground state of the QW with the contacts' Fermi energy. However, the energetic spacings of the levels within the QW, which are given by the QW width, remain unaffected by this modification.

Similar to the creation of the barriers in the conduction band, this modification is easily achieved by incorporating Cd into the QW. Since the CdSe bandgap is 1.74 eV at 4.2K, alloying Cd into the (Zn,Mn)Se offers a possibility to lower the QW conduction band edge. Because the bandgap of  $Zn_{1-x}Mn_xSe$  following Astakhov *et al.* [Asta 02] findings is given by

$$E_a(x) = 2.82 - 0.145x + 4.073x^2 (2.14)$$

for 8% of manganese the resulting energy gap of 2.83 eV is similar to the one of pure ZnSe. Hence the bandgap variation when Cd is incorporated into the QW can be expressed in terms of a  $\text{Zn}_x\text{Cd}_{1-x}\text{Se}$  alloy. According to Lunz *et al.* [Lunz 96] the change of the energy gap is given by

$$E_q(x,T) = E_q(0,T)(1-x) + E_q(1,T)x - ax(1-x)$$

(2.15)

where  $E_g(0,T)$  and  $E_g(1,T)$  denote the bandgaps of CdSe and ZnSe at a given temperature T and a includes the deviation from linearity.

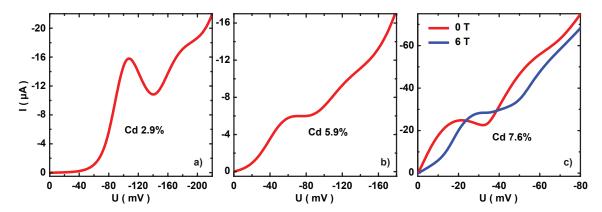

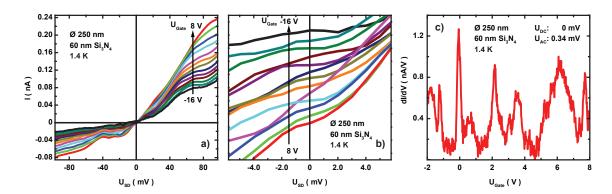

Figure 2.9 displays I-U curves of standard  $100^2~\mu\text{m}^2$  RTD devices with varying Cd concentrations in the 7 nm wide QW of 2.9%, 5.9% and 7.6%. The measurements clearly show that the resonance is shifting towards zero bias and reaches the linear transport regime at a Cd concentration of 7.6%. This behavior indicates that the ground energy state in the QW is finally situated near the contacts' Fermi energy, facilitating electronic transport when a small source drain bias voltage is applied. The observation of a single resonance moving to higher energies when a magnetic field is applied, as shown by figure

**Fig. 2.8:** I-U curves of  $100^2 \ \mu\text{m}^2$  RTD devices with varying  $\text{Zn}_{0.92}\text{Mn}_{0.08}\text{Se}$  quantum well thicknesses of a) 9 nm, b) 11 nm and c) 13 nm showing the decrease of the energetic position of the first resonance towards lower energies as the quantum well thickness is increased, as expected from figure 2.7. The alignment of the first resonance with the Fermi energy in the contacts is not achieved this way.

**Fig. 2.9:** I-U curves of  $100^2 \,\mu\text{m}^2$  RTD devices with a 7 nm thick  $\text{Zn}_{0.92-x}\text{Mn}_{0.08}\text{Cd}_x\text{Se}$  quantum well and a varying Cd incorporation of a) 2.9%, b) 5.9% and c) 7.6% showing the decrease of the energetic position of the first resonance towards lower energies as the Cd incorporation is increased. This way the alignment of the first resonance with the Fermi energy in the contacts is achieved.

2.9c, supports this interpretation. Since the downwards moving resonance remains below the Fermi energy, it can't be accessed in transport measurements. Furthermore the still existent PVR > 1 enables the reliable observation of the resonance peak, indicating a good confinement of the electron wave in the QW. A similar approach is also found in the final DBH from the III-V material system. Here the best results have been achieved by lowering the conduction band bottom using a  $In_{0.05}Ga_{0.95}As$  alloy through incorporation of In [Taru 96].

Having established an appropriate II-VI RTD heterostructure for the linear transport regime, as presented in figure 2.3, a fabrication method of gated vQDots from this semiconductor material is developed in this thesis.

# Chapter 3

# Contacting

The miniaturization of the RTD structure towards sub micrometer pillars is faced with new challenges in contacting the future three terminal device. In the following two issues and their solutions towards proper contacting are described. First, for all devices to be fabricated from the II-VI material system a simple and reliable contact separation has to be provided ensuring a current path solely through the device. In order to achieve this and given the starting material a suitable and reliable process step needs to be developed. Second, the few hundred nanometer wide pillar mesas, forming the vQDots, require proper contacting of their top. In this context the idea of metal capped insulating semiconductor line mesas [Aust 97] as an alternative top contacting method for sub micrometer pillars is investigated for our material system in terms of fabrication and conductivity, while being miniaturized. In addition to this the established air bridge technique [Borz 04], proving to be essential later in the vQDot fabrication process, is adjusted such that the device's non-planar surface can be accurately spanned.

## 3.1 Contact separation

The state of the art vQDots based on a RTD heterostructure are fabricated from the III-V material system [Kouw 01, Kita 07b]. Here high quality III-V wafers for MBE growth allow the utilization of the wafer backside as an electrical contact of the device. Unlike in the III-V material system there is no adequate II-VI wafer for MBE growth of the RTD structure used in this thesis. Due to the 0.27% lattice mismatch of ZnSe compared to GaAs [Oleg 87], the (Zn,Cd,Be,Mn)Se heterostructure is grown on a epi-ready GaAs wafer. Thereby a polar II-VI/III-V interface, caused by the different electron affinities of ZnSe and GaAs, is developed leading to the formation of electric fields and charging in the II-VI heterostructure [Farr 91, Frey 09]. The investigation of the n-ZnSe/GaAs heterointerface by Frey et al. revealed a depletion zone of 60 - 110 nm in the highly doped ZnSe-layer attributed mainly to the interdiffusion of atoms across the II-VI/III-V interface. As a result of this study a pseudomorphic II-VI buffer consisting of 200 nm of highly doped (Zn<sub>0.97</sub>Be<sub>0.03</sub>)Se ( $10^{19}$ cm<sup>-3</sup>), followed by five undoped periods of 50 nm ZnSe/20 nm (Zn<sub>0.9</sub>Be<sub>0.1</sub>)Se and terminated by 300 nm of undoped (Zn<sub>0.97</sub>Be<sub>0.03</sub>)Se has

28 3. Contacting

**Fig. 3.1:** The II-VI layer structure shows the composition of the superlattice and the dimensions of the different heterostructure segments.

been developed to eliminate the influence of electrical fields as well as charging from the pollar III-V/II-VI interface and screen away the interface effects from the relevant layers of the device. Figure 3.1 shows the II-VI heterostructure used in this thesis to fabricate vQDots which is built from the GaAs wafer, the detailed multilayer buffer and the DBH presented in chapter 2.2.

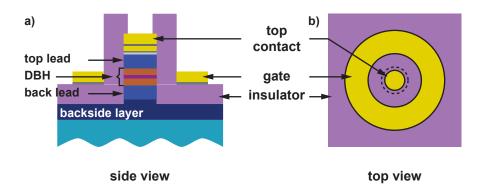

Given the layer configuration of the heterostructure two characteristics for future devices are included. First, as mentioned, compared with state of the art III-V vQDots the wafer backside is not usable for contacting, e.g. forming the source of the device [Taru 95]. Thus the corresponding contact has to be placed laterally on the highly doped ZnSe (2  $\times$   $10^{19} {\rm cm}^{-3}$ ) backside layer on top of the multilayer buffer. Second, the areas, comprising the bonding pads for the top contact and gate, have to be properly isolated against this highly doped ZnSe backside layer. Any electrical contact to this layer outside the pillar creates an additional path for electrons in parallel influencing any effect to be investigated. The isolation can be done either by deposition of insulator or by separating the different bonding regions by trenches. Due to the low height of the RTD heterostructure (  $\sim$  145 nm from the top of the backside layer ) and the thin injector regions ( 20nm at the bottom and 25 nm at the top ) only thin insulator layers can be deposited which can be easily damaged during the bonding process and thus causing unwanted shorts. The separation of the bonding areas by interrupting the backside layer however promises to be a better approach to avoid parallel conducting paths.

Considering the results of Frey et. al for the vertical transport through the multilayer buffer, also confirmed by own tests, separating the bonding pad areas down to the insulating GaAs buffer proves to yield a resistance  $\gg 1$  G $\Omega$  at 4.2 K in the + 200 mV to - 200 mV voltage range. Since in some test wafers it has been observed that the II-VI superlattice exhibited resistances in the range of some M $\Omega$  instead of several hundred M $\Omega$ , an etch stop in the multilayer buffer is insufficient. Under the consideration that sub micrometer pillars are expected to exhibit resistances > 100 M $\Omega$  an eventually non insulating superlattice causes electrical shorting. Therefore the separation of the bonding areas has to be etched down to the III-V buffer layer in order to guaranty full electrical insulation.

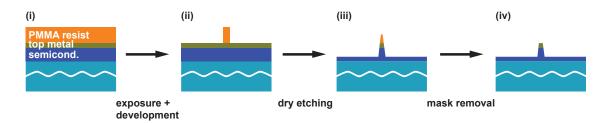

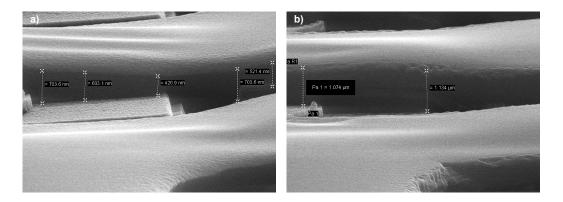

Given the II-VI heterostructure (fig.3.1) the depth of these disconnecting trenches needs to be > 1.3  $\mu$ m, measured from the *in situ* deposited top contact metal. However, the width of the notches depends on their position within the device structure. In the

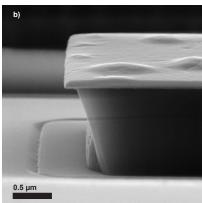

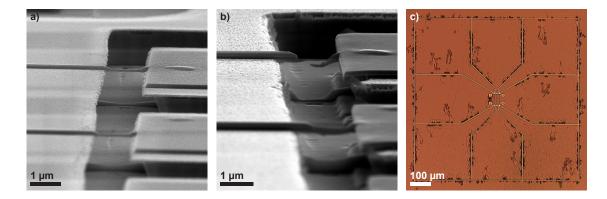

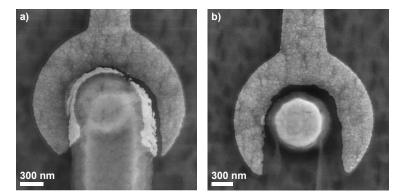

**Fig. 3.2:** SEM micrographs display different deep features being fabricated by a) dry etching and b) wet etching after a first dry etching step.

area near the pillar the width has to be about 1  $\mu$ m, whereas at the bonding pads 5  $\mu$ m wide ditches can be used. To carve these notches into the heterostructure either a dry etching method or wet etching is applicable. Due to its anisotropic character dry etching facilitates optimal pattern transfer with minimal lateral influence in pattern dimension (fig.3.2a). By contrast, the isotropy of wet etching in the II-VI heterostructure is unsuitable for the trenches near the pillar, where the width and depth have similar dimensions (fig.3.2b). In order to fabricate trenches the corresponding pattern has to be defined in a masking material, which has to satisfy the following requirements. First, the erosion of the mask should be minimal vertically and laterally entailing the use of masking materials with etching rates much smaller than the material to be removed. Second after finishing the etching process the mask has to be removable without leaving behind any residue influencing later processing steps or device functionality. Finally, the methods of removing the mask should not affect adversely the original material by etching or chemically alterating. Thus commonly used masking materials for dry etching of deep features are resists, dielectrics and metals.

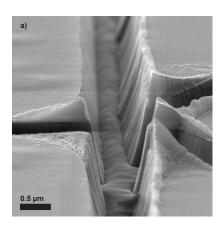

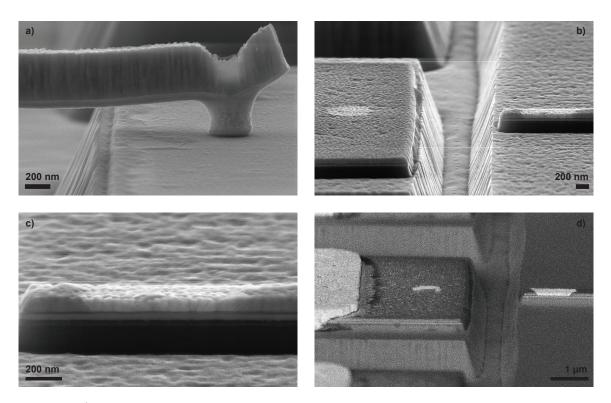

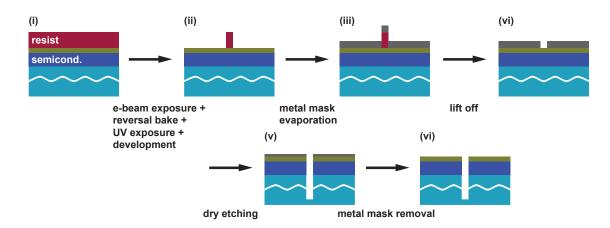

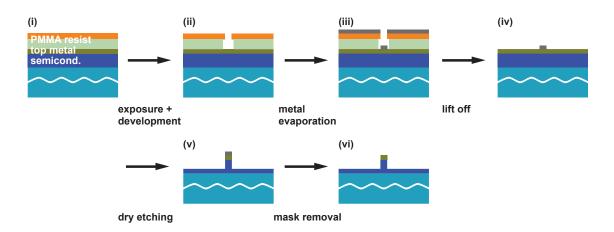

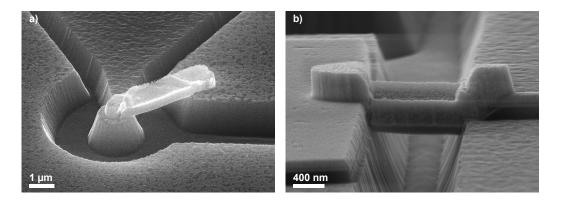

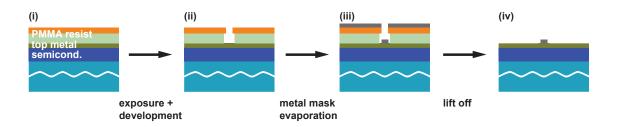

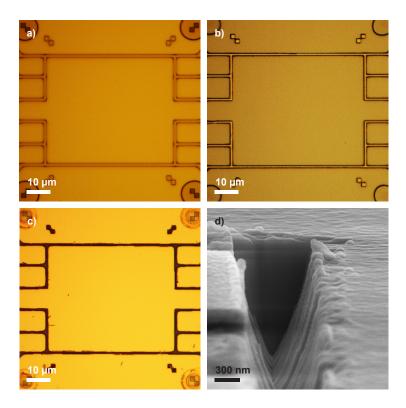

Based on the process for micrometer size RTDs presented by Borzenko et al. [Borz 05], requiring EBL, the trenches are fabricated by apply a PMMA positive resist mask. A sketch in figure 3.3a illustrates briefly the main process steps. The etching rate of the PMMA resist 950K (5%) for the CAIBE dry etching process of the ZnSe heterostructure is 11 nm/min over 70 nm/min for the semiconductor. Its thickness of about 480 nm when spun at 5000 rpm ensures the protection of the covered surface during the total etching time of about 18 min. Figure 3.3b and c show the PMMA masks for the two steps in etching trenches for micrometer sized RTDs following the recipe of T. Borzenko [Borz 05]. The quick and easy manufacturing of the necessary deep notches makes the fabrication step interesting for later testing structures as shown by figure 3.3d.

However, the disadvantages of this fabrication step evolve during the work on different testing and characterization devices which results in abandoning the resist mask for deep feature etching and developing a processing step for trenches utilizing Ti metal as a 3. Contacting

**Fig. 3.3:** a) A brief sketch showing a dry etching process using a positive resist mask. Optical images displaying the PMMA resist masks used in the b) 1st and c) 2nd fabrication step (mask shifted due to misalignment) following Ref. [Borz 05]. d) The red colored area is the resist mask used for dry etching the trenches in line mesa testing structures.

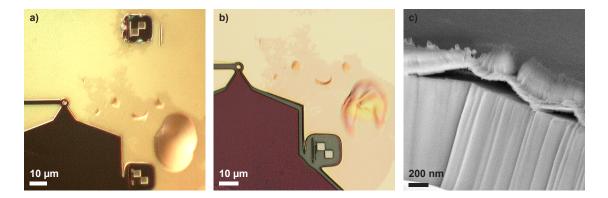

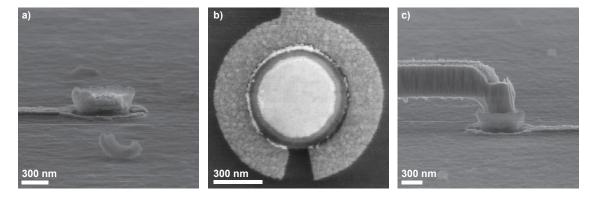

masking material. One downside of the PMMA mask arises from the difference in the heterostructure to be etched in comparison to the layer stack used in the first place by Borzenko et al. [Borz 05], which lacks the II-VI superlattice but has instead just a 300 nm thick high doped ZnSe  $(10^{19} \text{cm}^{-3})$  layer. The increasing distance between the backside layer and the insulating III-V buffer necessitates a longer total etching time leading to an extended exposure of the resist mask to Ar ion bombardment and BCl<sub>3</sub> radicals. The sustained ion bombardment hardens the resist surface impeding an easy removal by stripping chemicals and thus requiring heating and usage of continuous ultra sonic agitation. Figure 3.4a depicts the junction between a bridge post and its corresponding metal pad in a test sample for line mesas, being described later in this chapter. The residue from the deep feature etching step is still well observable on the metal surface at the end of the fabrication process. This fact is also confirmed by figures 3.4b - 3.4d recorded after a bridge, connecting a line mesa to its contact pad for bonding, has been accidentally riped off. For clarification, the actual bonding pad at the left most end, displayed in figure 3.4d, has been evaporated after the dry etching steps. The SEM images recorded with the secondary electron detector indicate the existence of an additional layer on the etched structures. In lens detector images of the same area show that these uncovered areas of gold have the same contrast as the bonding pads and bridges evaporated from gold added after the dry etching step. Thus the darkening of the bridge contact pad and the line mesa is attributed to the contamination by the previous deep feature etching step. Considering the fact that many of the samples containing a PMMA etching mask