#### Decentralized and Pulse-based Clock Synchronization in SpaceWire Networks for Time-triggered Data Transfers

#### Dissertation zur Erlangung des Doktorgrades der Naturwissenschaften

vorgelegt in der Fakultät für Mathematik und Informatik der Julius-Maximilians-Universität Würzburg

Autor: Kai Borchers

Gutachter:

Prof. Dr.-Ing. Sergio Montenegro Prof. Dr.-Ing. Görschwin Fey

Februar 10, 2020

I hereby declare that I have created this work completely on my own and used no other sources or tools than the ones listed, and that I have marked any citations accordingly.

Hiermit versichere ich, dass ich die vorliegende Arbeit selbständig verfasst und keine anderen als die angegebenen Quellen und Hilfsmittel benutzt sowie Zitate kenntlich gemacht habe.

Bremen, Februar 2020 Kai Borchers

## Acknowledgements

I would like to thank all the people who supported me throughout the years by either technical discussions or by motivating me to finish this project. Additionally, I am quite thankful for the excellent infrastructure of the DLR Institute of Space Systems, where I have had access to throughout all the years.

A special thanks goes to Sergio Montenegro and Görschwin Fey who agreed to spend a lot of their time in supporting me and reviewing this work.

Finally, I have to say rather sorry than thank you to my friends and especially to my family for whom I should have had more time.

### Abstract

Time-triggered communication is widely used throughout several industry domains, primarily for reliable and real-time capable data transfers. However, existing time-triggered technologies are designed for terrestrial usage and not directly applicable to space applications due to the harsh environment. Instead, specific hardware must be developed to deal with thermal, mechanical, and especially radiation effects.

SpaceWire, as an event-triggered communication technology, has been used for years in a large number of space missions. Its moderate complexity, heritage, and transmission rates up to 400 MBits/s are one of the main advantages and often without alternatives for on-board computing systems of spacecraft. At present, real-time data transfers are either achieved by prioritization inside SpaceWire routers or by applying a simplified time-triggered approach. These solutions either imply problems if they are used inside distributed on-board computing systems or in case of networks with more than a single router are required.

This work provides a solution for the real-time problem by developing a novel clock synchronization approach. This approach is focused on being compatible with distributed system structures and allows time-triggered data transfers. A significant difference to existing technologies is the remote clock estimation by the use of pulses. They are transferred over the network and remove the need for latency accumulation, which allows the incorporation of standardized SpaceWire equipment. Additionally, local clocks are controlled decentralized and provide different correction capabilities in order to handle oscillator induced uncertainties. All these functionalities are provided by a

viii Abstract

developed Network Controller (NC), able to isolate the attached network and to control accesses.

# Contents

| A            | ckno  | wledgements                             | v                      |

|--------------|-------|-----------------------------------------|------------------------|

| $\mathbf{A}$ | bstra | nct                                     | vii                    |

| Li           | st of | Figures                                 | $\mathbf{x}\mathbf{v}$ |

| Li           | st of | Tables                                  | xvii                   |

| A            | crony | yms                                     | xix                    |

| Ι            | In    | troduction and Motivation               | 1                      |

| 1            | Inti  | roduction                               | 3                      |

|              | 1.1   | Motivation and Background               | 3                      |

|              |       | 1.1.1 SpaceWire Issues                  | 4                      |

|              |       | 1.1.2 Event and Time-Triggered Networks | 5                      |

|              | 1.2   | Contribution                            | 5                      |

|              | 1.3   | Publications                            | 8                      |

|              | 1.4   | Thesis Structure                        | 8                      |

| Π            | F     | oundation                               | 11                     |

| 2            | Tin   | ne-triggered Communication              | 13                     |

|              | 2.1   | Introduction                            | 13                     |

|              | 2.2   | Digital Clocks                          | 16                     |

X Contents

|   | 2.3  | Clock uncertainties                       |

|---|------|-------------------------------------------|

|   | 2.4  | Accuracy versus Precision                 |

|   | 2.5  | Global Time                               |

|   | 2.6  | Start-up                                  |

|   | 2.7  | Integration                               |

|   | 2.8  | Clock Synchronization                     |

|   |      | 2.8.1 Processing Order                    |

|   |      | 2.8.2 Convergence Functions               |

|   |      | 2.8.3 Technology Specific Application     |

| 3 | Fiel | ld Programmable Gate Arrays 31            |

|   | 3.1  | Introduction                              |

|   | 3.2  | General Architecture                      |

|   | 3.3  | Radiation Effects                         |

|   |      | 3.3.1 Single Event Effects                |

|   |      | 3.3.2 Total Ionizing Dose                 |

|   | 3.4  | Design Flow                               |

|   | 3.5  | Formal Verification                       |

|   |      | 3.5.1 Equivalence Checking                |

|   |      | 3.5.2 Clk Domain Crossing                 |

|   |      | 3.5.3 Model Checking                      |

|   | 3.6  | Functional Simulation                     |

|   |      | 3.6.1 Constrained Random Verification 41  |

|   |      | 3.6.2 Languages                           |

|   | 3.7  | Assertion-based verification              |

|   | 3.8  | Universal Verification Methodology        |

|   |      | 3.8.1 Architecture                        |

|   |      | 3.8.2 SystemVerilog Assertion Integration |

| 4 | Spa  | aceWire 49                                |

|   | 4.1  | Introduction                              |

|   | 4.2  | Layers                                    |

|   |      | 4.2.1 Physical Layer                      |

<u>Contents</u> xi

|    |     | 4.2.2 Signal Layer                   | 50         |

|----|-----|--------------------------------------|------------|

|    |     | 4.2.3 Character Layer                | 51         |

|    |     | 4.2.4 Exchange Layer                 | 53         |

|    |     | 4.2.5 Packet Layer                   | 54         |

|    |     | 4.2.6 Network Layer                  | 55         |

|    | 4.3 | Extensions                           | 56         |

| II | Ι ( | Contribution                         | <b>5</b> 9 |

| 5  | App | proach and System Design             | 61         |

|    | 5.1 | Introduction                         | 61         |

|    | 5.2 | Pulse-based Remote Clock Estimation  | 62         |

|    |     | 5.2.1 General Approach               | 62         |

|    |     | 5.2.2 Concrete SpaceWire Utilization | 66         |

|    | 5.3 | System Architecture                  | 67         |

|    |     | 5.3.1 Host to NC Interaction         | 69         |

|    | 5.4 | Core Functionalities                 | 72         |

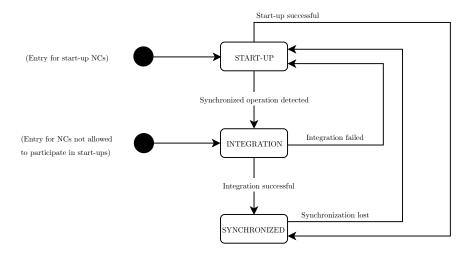

|    |     | 5.4.1 Start-up                       | 72         |

|    |     | 5.4.2 Integration                    | 74         |

|    |     | 5.4.3 Clock Synchronization          | 75         |

|    | 5.5 | Jitter Reduction                     | 80         |

| 6  | Bro | padcast Code Evaluation              | 83         |

|    | 6.1 | Introduction                         | 83         |

|    | 6.2 | Simulation Environment               | 83         |

|    | 6.3 | Formal Property Verification         | 85         |

|    |     | 6.3.1 Property Checking              | 86         |

|    |     | 6.3.2 Constraints                    | 89         |

|    |     | 6.3.3 Coverage                       | 90         |

|    |     | 6.3.4 Clk Modeling                   | 90         |

|    |     | 6.3.5 Complexity Handling            | 93         |

|    | 6.4 | Jitter Analysis                      | 97         |

|    |     | 6.4.1 Simulation-based               | 98         |

xii Contents

|              |            | 6.4.2 Formal-based         | 0 |

|--------------|------------|----------------------------|---|

|              | 6.5        | Conclusion                 | 5 |

| 7            | Syst       | tem Evaluation 10'         | 7 |

|              | 7.1        | Introduction               | 7 |

|              | 7.2        | Simulation Environment     | 7 |

|              |            | 7.2.1 Metric Analyzer      | 9 |

|              |            | 7.2.2 Design Checks        | 0 |

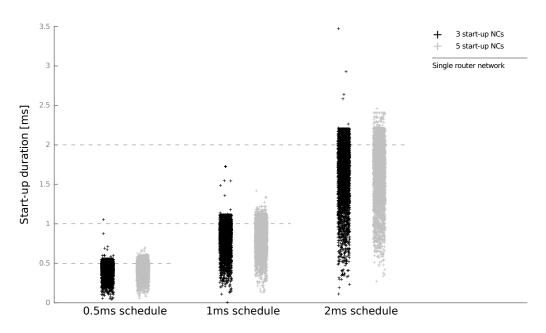

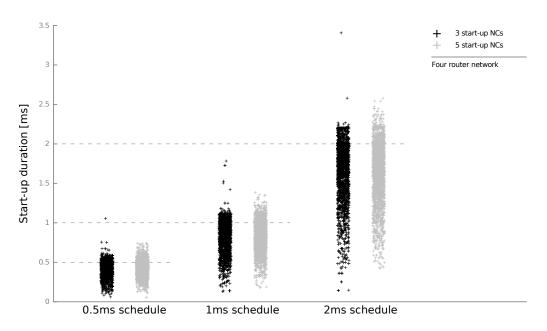

|              | 7.3        | Start-up Analysis          | 2 |

|              |            | 7.3.1 Execution Times      | 2 |

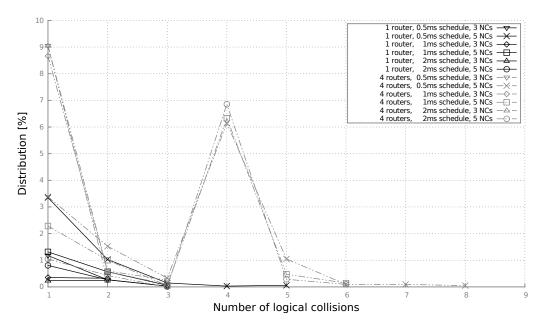

|              |            | 7.3.2 Logical Collisions   | 4 |

|              | 7.4        | Distributed Clock Analysis | 5 |

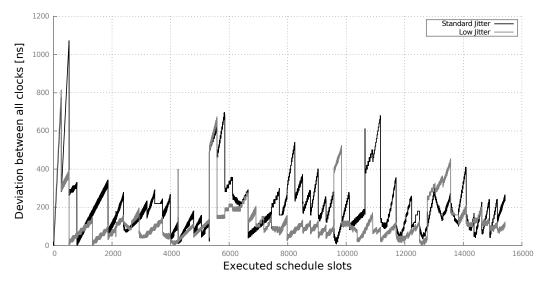

|              |            | 7.4.1 Deviation Over Time  | 6 |

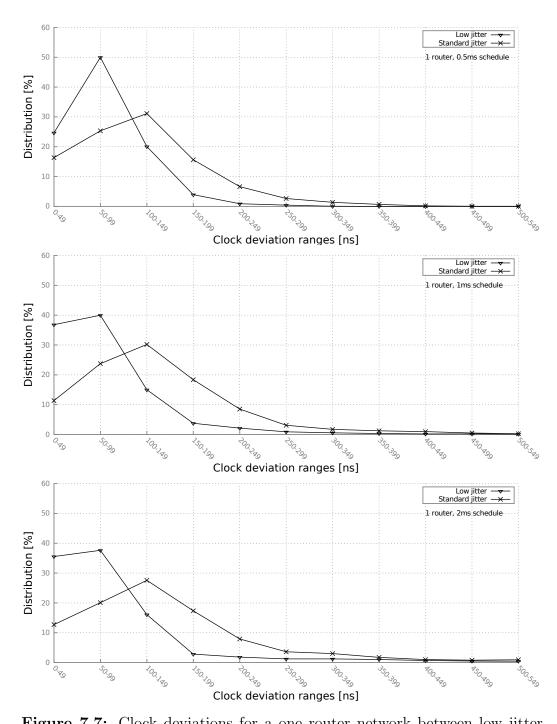

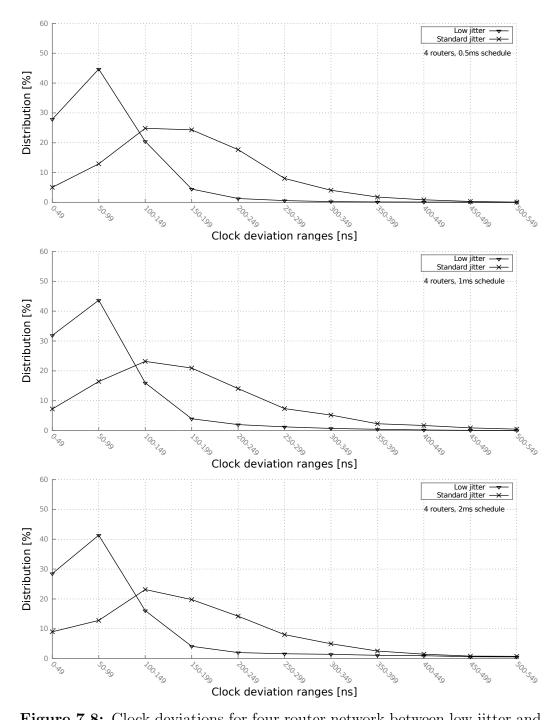

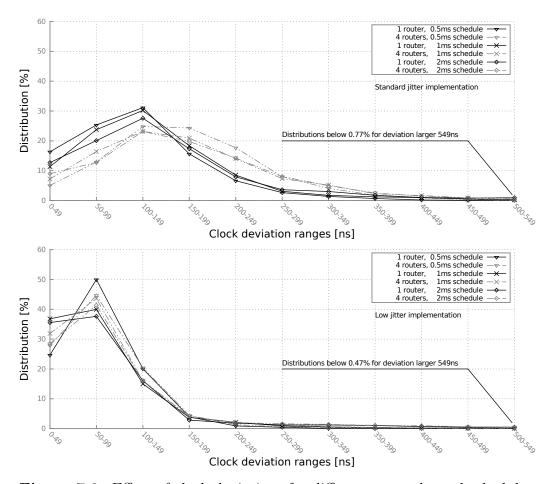

|              |            | 7.4.2 Distribution         | 8 |

|              | 7.5        | Target Utilization         | 3 |

|              | 7.6        | Conclusion                 |   |

| 8            | Out        | look 12'                   | 7 |

| IV           | 7 <u>A</u> | Appendix 129               | 9 |

| $\mathbf{A}$ | Not        | ations 13                  | 1 |

|              | A.1        | Introduction               | 1 |

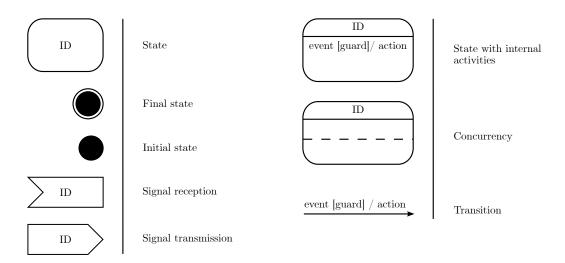

|              | A.2        | UML State Diagrams         | 1 |

|              | A.3        | Extended Backus-Naur Form  | 2 |

| Bi           | bliog      | raphy 13                   | 3 |

# List of Figures

| 2.1 | Typical structure of time-triggered systems                        | 14 |

|-----|--------------------------------------------------------------------|----|

| 2.2 | Network access depending on its topology                           | 15 |

| 2.3 | Digitalization error as a function of oscillator granularity       | 17 |

| 2.4 | Definition of precision and accuracy                               | 19 |

| 2.5 | Construction of schedule cycles based on microticks,               |    |

|     | macroticks and slots                                               | 20 |

| 3.1 | Basic FPGA architecture                                            | 33 |

| 3.2 | Typical circuit elements (combinational logic and flip-flops)      | 35 |

| 3.3 | High-level and register-transfer level synthesis flow              | 37 |

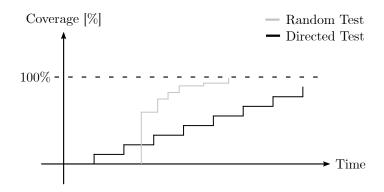

| 3.4 | Verification progress of random versus directed testing            | 42 |

| 3.5 | Basic UVM architecture                                             | 45 |

| 3.6 | Code example of an assertion check based on property and           |    |

|     | sequence definitions                                               | 46 |

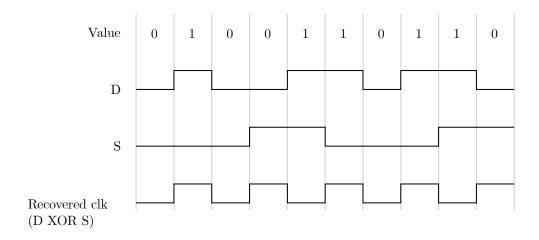

| 4.1 | Data-strobe encoding with recovered clk                            | 50 |

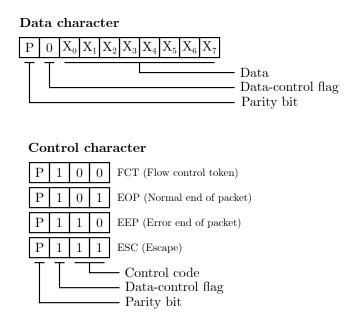

| 4.2 | SpaceWire data and control characters                              | 51 |

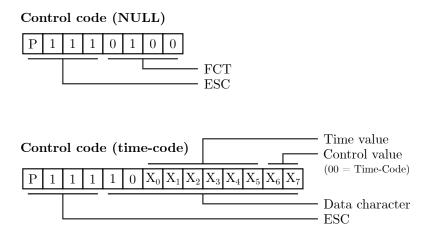

| 4.3 | Initially defined control codes (NULL and time-code) before        |    |

|     | actual SpaceWire standard revision                                 | 52 |

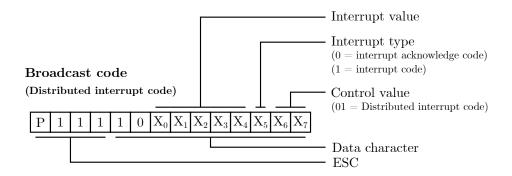

| 4.4 | Recently added distributed interrupt classified as broadcast code. | 53 |

| 4.5 | Structure of a basic SpaceWire packet                              | 55 |

| 4.6 | Prioritization problem for cascaded routers                        | 56 |

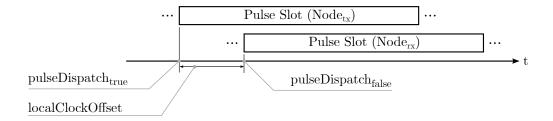

| 5.1 | Example schedule used to distribute time information               | 63 |

| 5.2 | Pulse reception for perfectly synchronized local clocks            | 63 |

xiv List of Figures

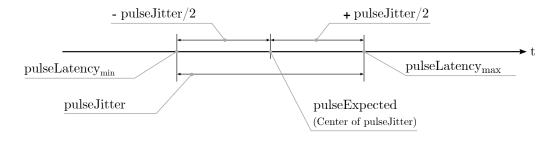

| 5.3  | Local clock drift effect on pulse determination 65                |

|------|-------------------------------------------------------------------|

| 5.4  | Distance from expected pulse location to jitter boundaries 66     |

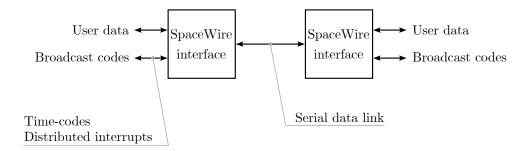

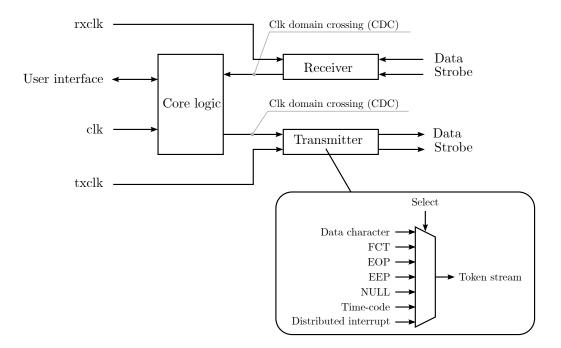

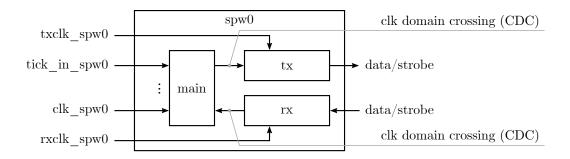

| 5.5  | SpaceWire interface connection with typical user interface 67     |

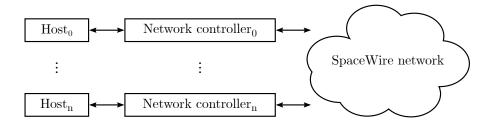

| 5.6  | Network controller based data exchange by utilizing SpaceWire     |

|      | networks                                                          |

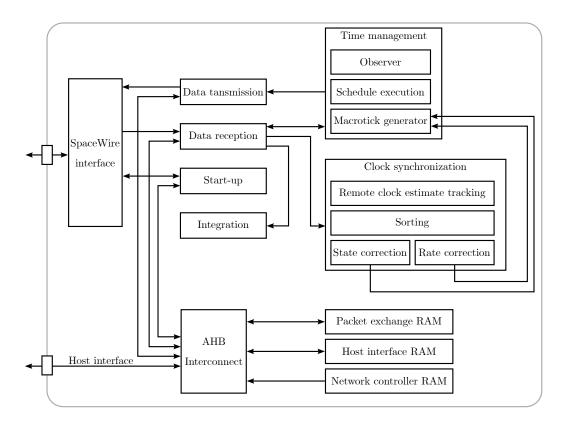

| 5.7  | Network controller structure                                      |

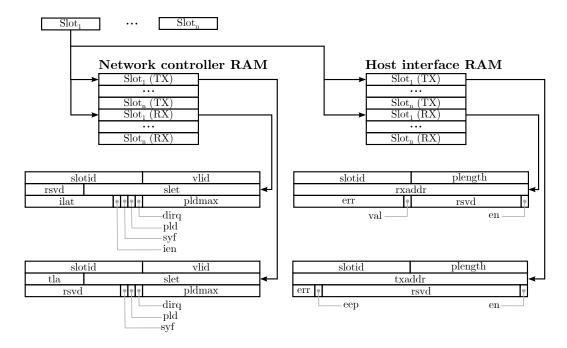

| 5.8  | Relation between schedule, network controller RAM, and host       |

|      | interface RAM                                                     |

| 5.9  | Network controller core functionalities                           |

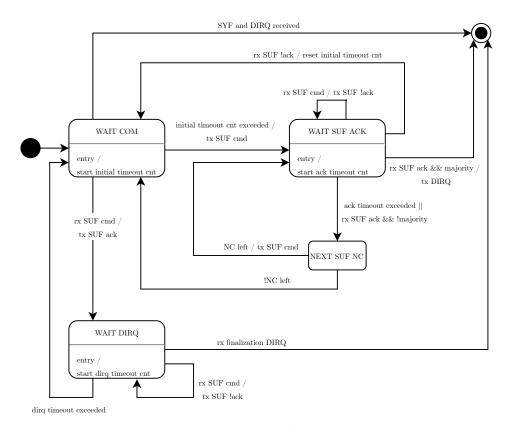

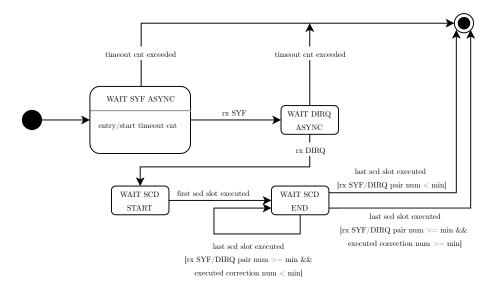

| 5.10 | Network controller start-up sequence                              |

| 5.11 | Network controller integration sequence                           |

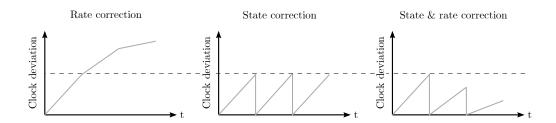

| 5.12 | Effect of different applied correction methods                    |

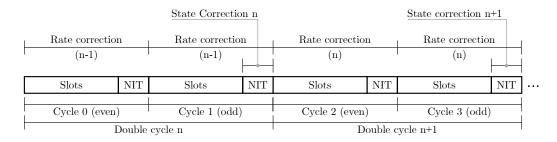

| 5.13 | Network controller schedule cycle structure                       |

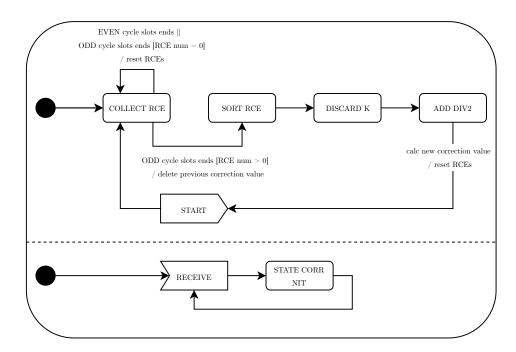

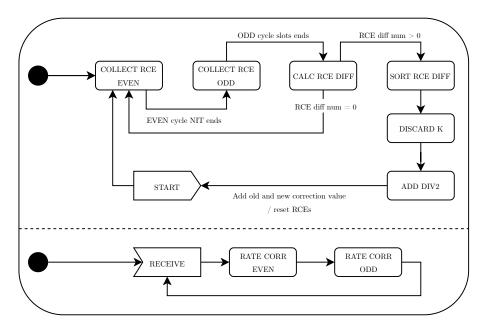

| 5.14 | Network controller state correction sequence                      |

| 5.15 | Network controller rate correction sequence                       |

| 5.16 | Character and code selection for the used SpaceWire interface. 80 |

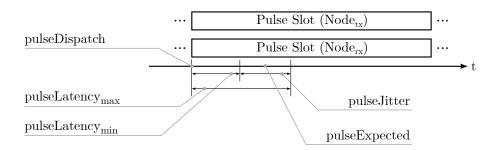

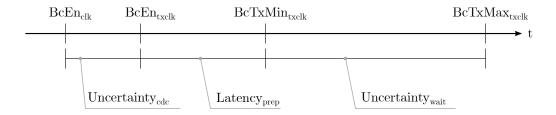

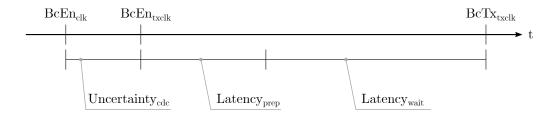

| 5.17 | Existing uncertainties and latencies for DIRQ transmissions 81    |

| 5.18 | Transfer of uncertainty into latency for low jitter DIRQ trans-   |

|      | missions                                                          |

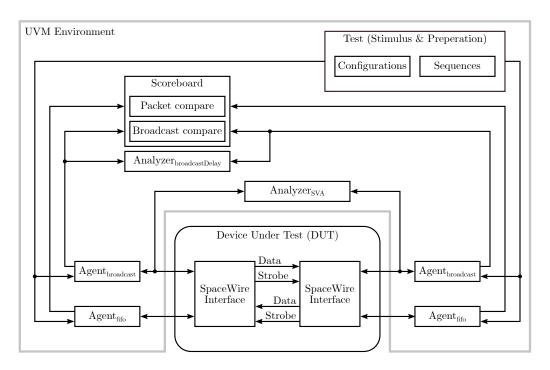

| 6.1  | UVM simulation environment used for DIRQ evaluation 84            |

| 6.2  | Specific simulation traces versus area investigation by formal    |

|      | property verification                                             |

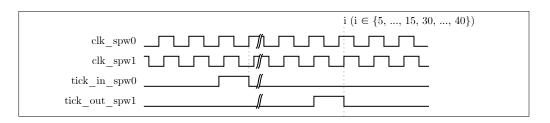

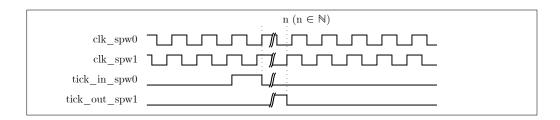

| 6.3  | DIRQ transmission with respect to different clk domains 87        |

| 6.4  | Concrete properties used to check distributed interrupt trans-    |

|      | mission durations for standard SpaceWire interface implemen-      |

|      | tations                                                           |

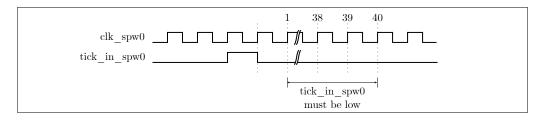

| 6.5  | Assumption used to ensure a minimum temporal distance be-         |

|      | tween two consecutive DIRQs                                       |

| 6.6  | Cover statement to track arbitrary DIRQ latencies 90              |

| 6.7  | Clk domains that are involved for all types of transmissions      |

|      | and receptions                                                    |

| 6.8  | Applied clk modeling for formal property verification 92          |

List of Figures xv

| 6.9  | Alternative clk modeling in order to adjust frequencies rather           |

|------|--------------------------------------------------------------------------|

|      | than phase relations                                                     |

| 6.10 | Assumption used to reduce state-space                                    |

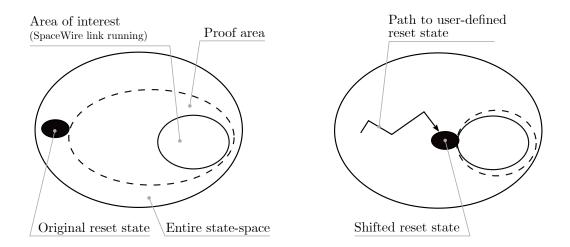

| 6.11 | Drastically reduced proof area due to user-defined reset state. 96       |

| 6.12 | Cover statement used to track initially all observed latencies 97        |

| 6.13 | Properties used to specify invalid latency areas                         |

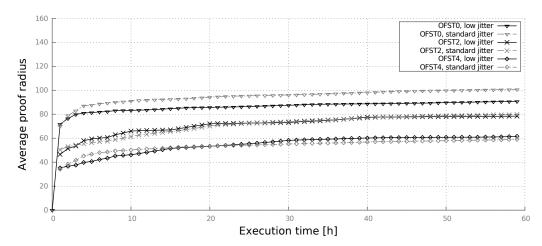

| 6.14 | Formal property verification progress over time for different clk        |

|      | modeling approaches                                                      |

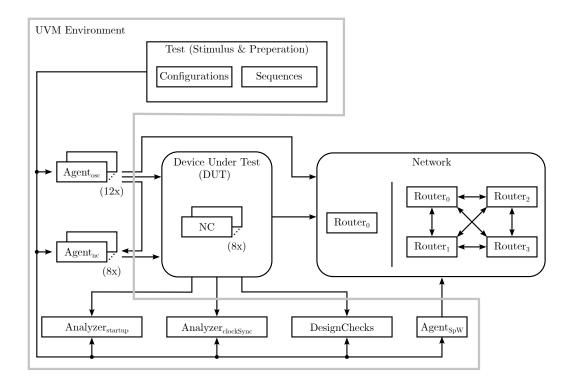

| 7.1  | UVM simulation environment used for system characterization. 108         |

| 7.2  | Microtick number check for odd schedule cycle executions $111$           |

| 7.3  | Tracked start-up durations for a network consisting of one router. $113$ |

| 7.4  | Tracked start-up durations for a network consisting of four              |

|      | routers                                                                  |

| 7.5  | Distribution of encountered logical collisions for all system con-       |

|      | figurations                                                              |

| 7.6  | Deviation of single traces as a function of executed schedule            |

|      | slots for a 2ms schedule and a four router network 117 $$                |

| 7.7  | Clock deviations for a one router network between low jitter             |

|      | and standard SpaceWire interface implementations                         |

| 7.8  | Clock deviations for four router network between low jitter and          |

|      | standard SpaceWire implementation                                        |

| 7.9  | Effect of clock deviations for different networks and schedules. 121     |

| A.1  | Subset of UML state diagram elements                                     |

# List of Tables

| 5.1        | Number of discarded values depending on valid remote clock                                                                             |

|------------|----------------------------------------------------------------------------------------------------------------------------------------|

|            | estimates                                                                                                                              |

| 6.1        | Blackbox effect on design size                                                                                                         |

| 6.2        | Simulation results for standard SpaceWire interface implemen-                                                                          |

|            | tations                                                                                                                                |

| 6.3        | Simulation results for low jitter SpaceWire interface implemen-                                                                        |

|            | tations                                                                                                                                |

| 6.4        | FPV coverage results for standard jitter implementations $101$                                                                         |

| 6.5        | FPV coverage results for low jitter implementations 102                                                                                |

| 6.6        | FPV property check results for standard jitter implementations.103                                                                     |

| 6.7        | FPV property check results for low jitter implementations 104                                                                          |

| 7.1<br>7.2 | Maximum deviations for all static evaluated configurations 122<br>Synthesis results for a single NC with different target devices. 123 |

| A 1        | Extended Backus-Naur Form (EBNF) operators 132                                                                                         |

## Acronyms

ABV Assertion-Based Verification

AHB Advanced High-Performance Bus

ASIC Application-Specific Integrated Circuit

BDD Binary Decision Diagram

BE Best-Effort

BFM Bus Functional Model

CDC Clk Domain Crossing

CM Compression Master

COTS Commercial Off-The-Shelf CRC Cyclic Redundancy Check

CRV Constrained Random Verification

C-state Controller State

CAS Collision Avoidance Symbol

CSMA/CD Carrier Sense Multiple Access/Collision De-

tection

CTL Computation Tree Logic

DIRQ Distributed Interrupt

DLR German Aerospace Center

DS Data-Strobe

DSP Digital Signal Processor

DUT Device Under Test

xx Acronyms

EBNF Extended Backus-Naur Form

EC Equivalence Checking

EDA Electronic Design Automation

EDIF Electronic Design Interchange Format

EEP Error End of Packet

EMC Electromagnetic Compatibility

EOP End Of Packet

ESA European Space Agency

ESC Escape

FCT Flow Control Token

FF Flip-Flop

FPGA Field Programmable Gate Array FPV Formal Property Verification

FV Formal Verification

HDL Hardware Description Language

HLS High-Level Synthesis

HVL Hardware Verification Language

IN Integration Frame

IP Intellectual Property

L-Char Link Character

LET Linear Energy Transfer LTL Linear Temporal Logic

LUT Look-Up Table

LVDS Low Voltage Differential Signaling

MC Model Checking

MOSFET Metal-Oxide-Semiconductor Field-Effect

Transistor

Acronyms xxi

MUL Multiplier

N-Char Normal Character NC Network Controller

NDCP Network Discovery and Configuration Proto-

$\operatorname{col}$

NIT Network Idle Time

NTP Network Time Protocol

OBC On-Board Computer

OVM Open Verification Methodology

PCB Printed Circuit Board PCF Protocol Control Frame

PPM Parts Per Million

PSL Property Specification Language

PTP Precision Time Protocol

QoS Quality of Service

RAM Random-Access Memory

RC Rate-Constrained

RCR Remote Clock Reading

RMAP Remote Memory Access Protocol

RTL Register-Transfer Level

ScOSA Scalable On-Board Computing for Space

Avionics

SEE Single Event Effect

SEFI Single Event Functional Interrupt

SEGR Single Event Gate Rupture

SEL Single Event Latch-up

xxii Acronyms

SET Single Event Transient

SEU Single Event Upset

SM Synchronization Master

SoC System-on-Chip SUF Start-Up Frame SV SystemVerilog

SVA SystemVerilog Assertions SYF Synchronization Frame

TDMA Time Division Multiple Access

TDP Time Distribution Protocol

TID Total Ionizing Dose

TMR Triple Modular Redundancy

TT Time-Triggered

TTCAN Time-Triggered Controller Area Network

TTEthernet Time-Triggered Ethernet

TTP/C Time-Triggered Protocol SAE Class C

UML Unified Modeling Language

UVM Universal Verification Methodology

VHDL Very High Speed Integrated Circuit Hardware

Description Language

VMM Verification Methodology Manual

# Part I Introduction and Motivation

## Chapter 1

### Introduction

#### 1.1 Motivation and Background

Communication technologies in spacecraft are essential as they connect all subsystems like On-Board Computer (OBC) or payload instruments together. In contrast to terrestrial systems, spacecraft engineers are limited in their selection of communication technologies. This limitation is mainly caused by radiation effects in space environments, which can lead to different undesirable impacts inside the selected hardware [KCR06]. These effects can range from Single Event Upset (SEU) were bit changes occur up to hardware disruptive events like Single Event Gate Rupture (SEGR). A special design and manufacturing process is often necessary to obtain the required resilience. However, the whole process of creating radiation hardened hardware can become very expensive and need to be reasonable from the economic point of view. Additionally, the space industry is quite small and far away from consuming as many electronic parts as commercial industries.

SpaceWire, as a communication technology for serial data transfers, was initially defined by the European Space Agency (ESA) in 2003. Since then, SpaceWire has been used in multiple projects throughout the whole space domain. One of its main advantages is the moderate complexity. This leads to a low utilization if used on a Field Programmable Gate Array (FPGA) or Application-Specific Integrated Circuit (ASIC) and also allows rapid develop-

4 1 Introduction

ment of SpaceWire components like interfaces or routers. The physical layer only requires Low Voltage Differential Signaling (LVDS) driver and receiver, whereas FPGAs and LVDS parts are both available as radiation hardened devices.

Recent projects that utilized SpaceWire are Eu:Cropis [Kot+18] and MAS-COT [Hab+13]. Both projects consist of a traditional spacecraft system structure with instruments centered around an OBC without real-time requirements. In contrast to these projects, the decentralized system Scalable On-Board Computing for Space Avionics (ScOSA) is developed inside the German Aerospace Center (DLR) [Tre+18]. It is based on a meshed SpaceWire network with different kinds of computing nodes and targets high performance, reliability, and scalability. These nodes can handle several tasks throughout different mission phases by the use of dynamic system reconfiguration. However, this reconfiguration property has a temporal boundary. As a consequence, real-time data transfers are required, which are not directly supported by SpaceWire.

Besides ScOSA, which is one reason for the research activities reflected in this work, we don't see a full replacement of SpaceWire within the next years.

#### 1.1.1 SpaceWire Issues

The SpaceWire standard does not support true real-time capabilities. One reason for this is the applied wormhole routing scheme [ESA08, p. 97]. This kind of routing allows message forwarding inside routers as soon as logical or path addresses are received. Wormhole routing will drastically reduce buffer sizes inside SpaceWire interfaces or routers but leads to messages that are spread throughout the whole network with the ability to block other data or creating deadlock situations.

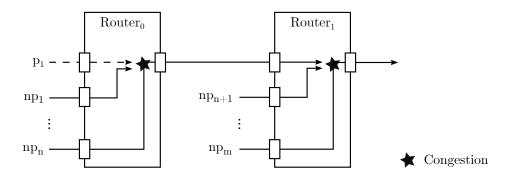

Priority based arbitration is proposed to establish at least basic Quality of Service (QoS) [ESA08, p. 99]. For this, logical addresses can be forwarded inside routers prioritized. However, cascading multiple routers can lead to situations where prioritized message forwarding doesn't work any longer [Bor+18]. Additionally, messages are allowed to have arbitrary lengths, which leads to

1.2 Contribution 5

undefined periods of network resource utilization.

#### 1.1.2 Event and Time-Triggered Networks

In general, communication networks can be classified in *time-triggered* and *event-triggered*. Communication inside event-triggered networks is established as soon as data is available. The inputs of the network can be considered as a trigger event. In contrast to that, time-triggered networks can only be accessed at specific points in time. These accesses are controlled by a static schedule, which is defined before time-triggered networks start their operation. This static schedule definition reduces the complexity of evaluating the network regarding performance and reliability.

Additionally, the schedule has a direct relation to the real-time capabilities of the network because all data transfers are controlled of it. This prevents conflicts of data transmissions between all participating units connected to the network and guarantees data delivery in time. Real-time capabilities can also be established in event-triggered networks by using a *rate constrained* approach. For this, the data bandwidth is limited by applying minimal idle times between consecutive data packets and by defining a maximum packet length [Boy+16].

#### 1.2 Contribution

This work addresses the SpaceWire real-time problem by developing a time-triggered approach for decentralized system structures. For this, a system-wide clock synchronization can be considered as a precondition. Existing clock synchronization approaches for meshed network topologies can't be applied directly without a non-standard modification of existing SpaceWire components. The problem is solved by a transfer of bus-based clock synchronization approaches into the SpaceWire networks as outlined more detailed in the following.

The first research contribution of this work is the development and implementation of new methods to handle start-up phase and clock synchronization 6 1 Introduction

in order to support distributed system structures for SpaceWire networks.

Both methods rely on the *broadcast code* feature of SpaceWire without the need to modify existing routers beyond the currently revised SpaceWire standard [ESA19]. These broadcast codes can be considered as system-wide interrupts, whereas its latency and jitter characteristics are directly correlated to the alignment of all local clocks which need to be synchronized.

A start-up phase is required to establish initially a system-wide or global time, which is a precondition for any kind of time-triggered data transfer. The implementation is based on a majority determination between multiple start-up involved nodes. The process is designed to tolerate n failing nodes, whereas n depends on the number of start-up nodes. The node, which is elected to finish a start-up phase, uses a broadcast code to align the initial set of local clocks. However, the quality of initial alignment requires an application of correction value, which depends on network structure and communication links.

An already established global time needs to be synchronized throughout schedule based operation. Otherwise, schedules would drift apart, which leads to a complete loss of communication. The synchronization process requires knowledge about the values of all other clocks that are part of the clock ensemble. These values are often derived in bus-based communication technologies by comparison between expected and actual reception of messages. However, this is only possible because of constant latencies, which is an implication of the network structure. Latencies can vary drastically in switched networks, which makes the bus-based approach impracticable. Instead, packets contain the accumulated delay throughout the whole path from source to destination node. Based on this accumulated value, the destination node can derive the required information of the source node clock. However, the accumulation requires that each unit, which is traversed by a packet, can determine these delays.

SpaceWire, with its switched network topology, would require a nonstandard redesign of its components if latency accumulations are selected to apply existing synchronization approaches. Instead, the bus-based approach is transferred into SpaceWire networks by utilizing broadcast codes 1.2 Contribution 7

to keep variations of latencies in a tolerable range. This allows the usage of existing SpaceWire components to create systems that can synchronize their clocks. The developed approach provides the ability of decentralized clock synchronization, which is a significant difference to the existing extension SpaceWire-D.

Additionally, a potential non-standard modification was applied to the used SpaceWire interface in order to change its broadcast code handling. The modification leads to a transfer of jitter into a larger but more constant latency with the intent of improving the clock synchronization quality.

The second research contribution covers the broadcast code evaluation concerning its latency range. The latency range defines the jitter, which is vital to get a proper clock synchronization. Hence, a Universal Verification Methodology (UVM) verification environment is created to transfer large numbers of broadcast codes in order to track all encountered latencies. These test runs are applied to standard and modified SpaceWire interfaces. Additionally, formal property verification is applied to get a confirmation of the functional simulation results provided by the UVM environment. However, the application of this formal approach leads to specific issues and limitations that are discussed in the related chapter.

The last research contribution focuses on the evaluation of the developed methods. For this, a complete time-triggered network with different structural configurations and several schedules were created as Very High Speed Integrated Circuit Hardware Description Language (VHDL) design. All relevant statistics were monitored and extracted by a UVM verification environment during multiple test runs. The results show that each applied start-up phase finished successfully with a neglectable number of logical collisions and within an acceptable time. The evaluation of clock synchronization shows that oscillator drifts were compensated, and local clock deviations don't exceed 1.2  $\mu$ s. However, the maximum clock deviation depends on multiple system parameters. Thus, the monitored maximum value of 1.2  $\mu$ s can't be treated as an overall upper boundary. An advantage of the modified SpaceWire interface with respect to synchronization quality was observed throughout all executed tests.

8 1 Introduction

#### 1.3 Publications

This work contains parts, extensions, or ideas of previously published material of the author<sup>1</sup>. A complete list of all publications is given in the Appendices IV. However, the following peer-reviewed papers are mainly considered for this thesis:

- The concept of the pulse-based and decentralized clock synchronization approach was introduced in [Bor+18].

- The prototype and first evaluation results were published in [Bor+19]. It contains the investigation of different system characteristics (e.g. start-up behavior or clock synchronization quality) and utilization results.

- The system evaluation was mainly done by functional simulation with the support of SystemVerilog Assertions. An alternative use case of SystemVerilog Assertions in order to handle volatile registers was discussed in [BMD19].

#### 1.4 Thesis Structure

The thesis is separated into four main parts. Part I provides a motivation and background information about the theses subject. Part II gives an overview of existing technologies and approaches which are applied inside this work. Chapter 2 covers the basic concepts and operational modes used in current time-triggered technologies. An overview of FPGAs regarding its structure and design flow is given in Chapter 3. Additionally, several FPGA verification aspects and methodologies are introduced. The foundation part closes with Chapter 4 by providing an overview of the communication technology SpaceWire. Its unique broadcast code capabilities are the backbone for the prototype developed in this work.

<sup>&</sup>lt;sup>1</sup>The author's birth name is Stohlmann.

9

The main contribution of this work is given in Part III. An introduction of the general clock synchronization approach is given in Chapter 5. It illustrates how remote clock estimates are gathered based on pulses and shows the architecture of the developed prototype. A modified SpaceWire interface is discussed as well to achieve an improved clock synchronization.

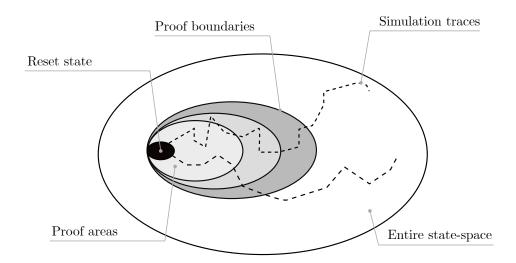

SpaceWire broadcast codes are evaluated separately in Chapter 6. They are the foundation of the introduced clock synchronization approach, whereas they are characterized in two different ways. Functional simulation with a constrained random approach is used on one side. On the other hand, formal property verification is applied in order to confirm or disproof the simulation-based results. Additionally, formal property verification specific problems (e.g. complexity handling) are discussed.

The overall system evaluation of the developed prototype is given in Chapter 7. It starts with an introduction of the UVM verification environment and its main components like metric analyzer and design checking parts. The system evaluation is divided into start-up and distributed clock analysis followed by an overview of synthesis results for different FPGA targets. Possible improvements and further work are discussed in Chapter 8. Finally, all used references and some notations are given in Part IV.

# Part II

# Foundation

## Chapter 2

## Time-triggered Communication

#### 2.1 Introduction

Accesses to communication mediums need to be managed in some way. A well-known access method is Carrier Sense Multiple Access/Collision Detection (CSMA/CD), used by the Ethernet protocol. It provides the ability to detect collisions in case two or more parallel messages are transmitted. Additionally, it resolves collisions by applying timeouts before retransmission of collided data. Time-triggered communication applies the Time Division Multiple Access (TDMA) access method to achieve a controlled, decentralized, and collision-free access to the communication medium. This kind of communication relies on the progression of a global time. Each node, required to transmit data, is allowed to access the network at specific points in time. These access points are defined by static schedules, stored locally at every node, and computed before the network starts operation. This kind of network access is considered as decentralized. In contrast to that, a network controlled by a single arbiter or master has a centralized access.

The executed clock synchronization approach is a major characteristic of each time-triggered technology. A distributed approach is present if multiple nodes exchange their clock values in order to derive a converged clock correction value. A centralized clock synchronization is applied if a single source is used to adjust all clocks inside the system. However, this represents a single point of failure, capable of causing a full loss of communication. This problem is unacceptable for most time-triggered technologies which are designed to provide high reliability or even being used in safety-critical systems. An example of this kind of technology is Time-Triggered Protocol SAE Class C (TTP/C). It was developed to fulfill requirements for distributed safetycritical systems in various domains like automotive or aerospace [TTT02, p. 11].

However, the distributed clock synchronization approach substantially increases system complexity. It requires an initial clock synchronization after system resets or power cycles to switch from an asynchronous to synchronous operation. Throughout synchronous operation, all local clocks need to be synchronized periodically to compensate drifts that occur over time. Finally, late powered or reset nodes require a re-integration into the existing synchronous operation.

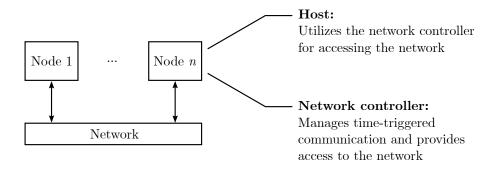

The typical structure of a time-triggered communication system is given in Figure 2.1. It consists of multiple nodes connected to a network for exchanging

Figure 2.1: Typical structure of time-triggered systems.

information. This network must be considered as a shared resource between all connected nodes. It's in the responsibility of the network controller to ensure all accesses are performed according to the schedule to prevent conflicts. A specific interface, often implemented as a descriptor table, allows the host to provide data for transmission to the network controller. A direct connection between host and network doesn't exist. Additionally, the network 2.1 Introduction 15

controller handles the start-up, clock synchronization, and integration tasks.

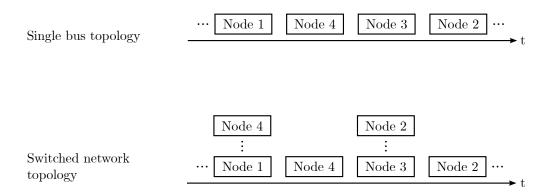

The network itself can consist of arbitrary structures and topologies. The structure has a direct impact on the schedule and how the network is accessed. Figure 2.2 shows two example schedules for bus and switched network topolo-

Figure 2.2: Network access depending on its topology.

gies. Each schedule consists of four slots utilized by one or more nodes. The bus topology allows only single access at the same time, indicated by an exclusive utilization of each slot. A multicast transmission with one source and n destinations is implicitly given. Several bus-based technologies like TTP/C [TTT02, p. 37], SAFEbus [HD92] or FlexRay [Rau07, p. 127] are available. All of them can be used with dual redundant channels to increase either data throughput or reliability.

Switched networks can be set up in a way that multiple accesses at the same time are possible. This multiple write property is given as soon as several data paths throughout the network are available. An example technology, that relies on the IEEE 802.3 Ethernet standard, is Time-Triggered Ethernet (TTEthernet) [TTT11, p. 6]. TTEthernet defines traffic classes to distinguish between different communication modes, whereas Time-Triggered (TT) has the highest priority. Additionally, Best-Effort (BE) and Rate-Constrained (RC) traffic classes for less or even none critical timing requirements are defined [Ste+09]. All these traffic classes share the same network throughout system operation.

Additional time-triggered communication aspects are discussed in the remainder of this chapter, which is structured as follows. Initially, the concept of digital clocks is introduced in Section 2.2 followed by a discussion of clock uncertainties in Section 2.3. A differentiation between clock accuracy and precision is given in Section 2.4 because of its importance to determine the quality of clock synchronization. The notion of global time with respect to distributed systems is given in Section 2.5. Finally, the main operational states are explained that most time-triggered technologies have to execute. An overview of start-up processes and how they are used to establish a global time is introduced in Section 2.6. Possible node integration strategies are shown in Section 2.7 followed by an introduction of different clock synchronization approaches in Section 2.8.

# 2.2 Digital Clocks

Clocks generally need periodic events and a mechanism to count them. A number of periodic events must be recognized depending on the duration that needs to be measured. Microwave based atomic clocks have been used to define a second since 1976 because of their superior performance. With the occurrence of optical-based atomic clocks, even higher accuracies are achievable [McG+19]. Optical clocks are also subject to research activities regarding synchronization within the femtosecond area [Ber+19]. However, generally electronic oscillators<sup>1</sup> are used for embedded systems in order to create periodic events. They fit in size and reliability with the disadvantage of being less accurate compared to atomic clocks.

For time-triggered systems, these periodic events are also called *microticks*, whereas the distance between two consecutive microticks is called *granule*. The granule can also be considered as the period T of an oscillator, which is defined as the reciprocal of its frequency f. To describe clocks and properties throughout definitions, the following notation  $property_i^k$  is applied, whereas k indicates the number of a clock and i represents a specific microtick or

<sup>&</sup>lt;sup>1</sup>Also indicated by term *clk* for the remainder of this work.

macrotick/tick<sup>2</sup>.

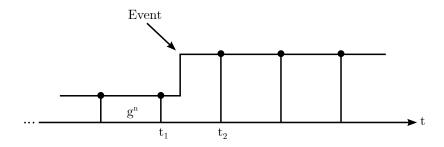

The granularity of a clock can only be measured with a clock that provides a finer granularity. However, each measurement by use of an electronic oscillator leads to digitalization errors, as shown in Figure 2.3.

Figure 2.3: Digitalization error as a function of oscillator granularity.

A signal value is sampled continuously by clock n to observe events. The event, indicated by an increase of signal value, takes place between  $t_1$  and  $t_2$ . A temporal deviation between real and recognized event occurs caused by the sampling rate with a maximum absolute error value of  $\frac{g^n}{2}$ . The error value can be decreased by selecting oscillators with higher frequencies, which leads to a shortened granule  $g^n$ . Another limitation of digital clocks is related to event ordering. The order of multiple observed events between two consecutive sampling points can't be reconstructed.

## 2.3 Clock uncertainties

Digital clocks are derived by use of oscillators as introduced in the prior Section 2.2. Hence, uncertainties of used oscillators directly correlate with the quality of digital clocks. These uncertainties are generally defined in Parts Per Million (PPM), which expresses the maximum deviation to the nominal oscillator frequency. Additionally, PPM values depend on different properties like temperature, voltage or aging [Vec17, p. 11].

<sup>&</sup>lt;sup>2</sup>A detailed definition of macrotick/tick is given in Section 2.5.

The *drift* of a clock can be defined with respect to two consecutive microticks by the following equation [Kop11, p. 54].

$$drift_i^k = \frac{z(microtick_{i+1}^k) - z(microtick_i^k)}{n^k}$$

(2.1)

It is assumed that all microticks of clock k are observable by clock z with a negligible digitalization error. This observation provides an actual duration between  $microtick_{i+1}^k$  and  $microtick_i^k$ , which contains a deviation to the nominal duration, expressed by  $n^k$ . The ratio between the actual and nominal duration of two consecutive microticks defines the drift for a given clock and a specific microtick.

Inside existing literature, the term *drift rate* is often used to express oscillator uncertainties. It can be defined by the following equation [Kop11, p. 55].

$$\rho_i^k = \left| \frac{z(microtick_{i+1}^k) - z(microtick_i^k)}{n^k} - 1 \right|$$

(2.2)

The drift rate describes an unsigned measure for the oscillator frequency deviation compared to its nominal frequency. A perfect oscillator without any deviations has a drift rate of 0.

# 2.4 Accuracy versus Precision

The *precision* is used to determine how close a clock ensemble is synchronized. The definition of precision requires an introduction of offsets between clocks. An offset is measured between two clocks j and k with the same granularity for a given microtick i by use of a reference clock z [Obe11, p. 15].

$$offset_i^{jk} = \left| z(microtick_i^j) - z(microtick_i^k) \right|$$

(2.3)

The digitalization error of reference clock z is considered as negligible. The maximum offset between n clocks for a given microtick i is defined as follows [Obe11, p. 15].

$$\Pi_i = \max_{\forall 1 \le j, k \le n,} \{offset\}$$

(2.4)

$\Pi_i$  represents the precision for a clock ensemble at microtick *i*. The precision for an arbitrary microtick interval is defined as  $\Pi$ . The precision values are expressed by microticks of the reference clock.

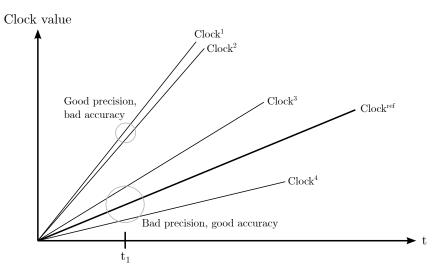

Clock deviations, measured to a given reference clock, are called *accuracy*. Similar to precision, the accuracy is also determined for a single microtick i but also for an arbitrary interval. Figure 2.4 shows the differences between precision and accuracy for a specific point in time.

Figure 2.4: Definition of precision and accuracy.

$Clock^1$  and  $Clock^2$  have a low offset between each other at  $t_1$ , which leads to a good precision between them. However, the offset of each clock to the reference  $Clock^{ref}$  is large, which causes a bad accuracy.  $Clock^3$  and  $Clock^4$  illustrates the opposite by showing a large offset between each other but a small offset to  $Clock^{ref}$ .

# 2.5 Global Time

As explained in Section 2.1, each node inside distributed systems generally has to maintain its own clock locally, whereas the value of its clock is derived by an oscillator. These oscillators can vary between nodes in frequency and stability. Thus, microticks of oscillators are insufficient to define a global time throughout all nodes.

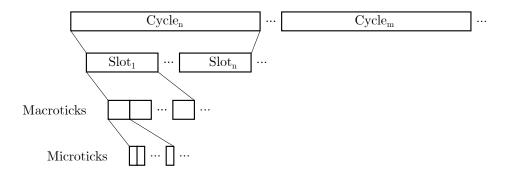

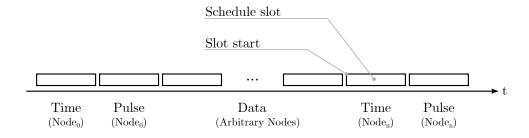

Instead, a system-wide temporal duration, often called *macrotick*, is defined [Cen+13, p. 33]. These macroticks are used to define parameters that are shared inside the whole system, e.g. slot lengths or whole schedules/cycles, as shown by Figure 2.5. They are derived by counting microticks until

**Figure 2.5:** Construction of schedule cycles based on microticks, macroticks and slots.

the defined macrotick duration is reached [Han06] and represent the smallest time granularity inside the system. The number of microticks per macrotick can vary between nodes depending on the used oscillators. This number can also vary for a single node as soon as correction methods for clock synchronizations are applied.

# 2.6 Start-up

A time-triggered system is considered as asynchronous after a global power-on or in case unexpected faults lead to a full loss of synchronization. The system changes to synchronous operation as soon as two or more nodes synchronize 2.6 Start-up **21**

their local clocks in order to execute their schedules. It is the responsibility of start-up algorithms to establish a synchronized time within a maximum temporal duration for a subset of nodes. The start-up phase is generally implemented separately to other processes to encapsulate its high complexity. Additionally, the separation allows a better exchange of the algorithm if required and improves maintenance and testability.

The implementation of a start-up process directly depends on the network topology. Three different start-up algorithms for a bus, with up to nine nodes, were described and evaluated in [Loe99] by use of simulation. Another start-up solution, based on unique message lengths, is provided by [CLS04]. A start-up algorithm and related architectural guidelines are provided in [SP02] with a focus on bounded execution durations and the ability to work under different failure scenarios. An extension in the fault hypothesis, which allows arbitrary failures, is discussed in [SK06]. Additionally, this enhanced algorithm was compared with the FlexRay start-up algorithm. It turned out that FlexRay is vulnerable to simple failure modes.

Bus-based start-up algorithms basically work in a similar way. A set of nodes, which are allowed to perform a start-up, exchange messages to establish the synchronous operation. For this, start-up nodes are initially passive by observing the bus to check for data exchanges that are already in progress. These data exchanges indicate that either synchronous operation is already performed or another start-up node executes a start-up phase to establish a synchronous operation. If no data exchanges are monitored throughout a timeout period, start-up nodes become active by starting their own local clock to provide periodically start-up specific data according to the schedule. These data, in turn, are used by other start-up nodes to determine the currently executed schedule position. This information is finally used by unsynchronized nodes to change into a synchronous operation.

Possible collisions must be handled during the asynchronous operation because no centralized mechanism is used to bring the system into a synchronous operation. Instead, multiple start-up nodes can begin their start-up phases in parallel. However, a bus topology only provides mutual exclusive write access. Thus, collisions need to be detected and resolved in some way.

The technology FlexRay detects collisions by use of the schedule [Fle10, p. 173]. Initially, a Collision Avoidance Symbol (CAS) is transmitted to the bus before start-up nodes start their local clocks to enter a reduced schedule execution for active start-up phase application. Throughout one reduced schedule execution, only a single start-up frame is transmitted per start-up node inside a unique slot. This CAS application can happen in parallel, whereby multiple start-up nodes start the schedule execution. This leads to several transmitted start-up frames throughout a single schedule execution. However, each start-up node is assigned to a unique slot for start-up frame transmission. Thus, all start-up frames are transmitted in a predefined order. The first start-up frame inside this order is recognized by all start-up nodes, which indicates a parallel start-up phase. By this, the collision is detected, and all start-up nodes that don't belong to the first start-up frame stop its active start-up phase. Start-up nodes, who canceled their start-up phase, observe again the bus to detect data transfers. The timeout used for observation is equal for all start-up nodes inside a FlexRay system.

TTP/C uses a different strategy to resolve collisions compared to the equal timeout of FlexRay. In case two or more start-up nodes start transmission within a specific interval, frames collide and are recognized as noise at the receivers [SP02]. The detection of noise leads to a reset of the timeout, which is used for observing the bus. These timeouts are unique for every start-up node. Thus, it is assumed that collisions resolve only by temporal differences introduced by unique timeouts.

Bus-based time-triggered technologies with their broadcast abilities rely on nearly constant message propagation delays for start-up, clock synchronization, and integration. Switched network topologies instead can't use the same concepts. Message delays can vary significantly caused by routing and congestion with a dependability to the network structure. Additionally, message multicasting is not necessarily applied. TTEthernet, as a prominent switched network technology, accumulates propagation delays inside transferred messages to overcome the problem. A request/acknowledge based data exchange between multiple participants is done throughout start-up phases to establish an initial time [TTT11, p. 53]. Thereby, the start-up routine differs for high

reliable configurations.

Algorithm analysis is often done by functional simulation. However, functional simulation is often not capable of checking all system properties concerning system states or state transitions. Formal verification can be applied to provide a mathematical proof that system properties hold under every defined condition. Such a formal verification was done for the DACAPO and TTP start-up algorithm in [LP97]. TTEthernet functionality, with respect to clock synchronization and start-up behavior, was investigated by formal verification in [SD11] and extended in [Dut+12]. A survey of additional formal verifications used for start-up algorithms, like TTCAN, SPIDER, or FlexRay, is given in [SRR16].

# 2.7 Integration

Nodes need to be integrated into synchronous operation in case they are powered on late, loss of synchronization due to errors or reset throughout operation. For this, an integrating node has to determine the actual system state to bring its own state in synchronicity. This state, or at least the relevant sub-state, is typically provided by data frames of already synchronized nodes periodically throughout synchronous operation. These data frames can be either dedicated or combined ones. Dedicated data frames used for integration reduces the overhead with the disadvantage of utilizing schedule slots. Combined data frames increase the overhead but don't block schedule slots. Typically, most technologies use synchronization frames also for integration.

FlexRay provides a single frame type to cover all functionalities [Fle10, p. 183], including payload transfers. The *startup frame indicator field* inside the header is used for integration, leading, and following start-up as well. This bit is set to one a single time by a subset of nodes throughout each schedule execution.

Different frame types are used by TTP/C. A separated frame for the startup and so-called normal frames for synchronous operation are used. Normal frames are further distinguished because they contain either implicit or explicit Controller State (C-state) information [Obe11, p. 98], which represents the system state. Implicit C-state information are only included into the frame Cyclic Redundancy Check (CRC). Already synchronized nodes must use their own C-state to verify the frame by calculating the CRC. However, the C-state can't be extracted from the frame, which makes the integration of unsynchronized nodes impossible. Explicit C-state frames instead, contain all required state information to perform an integration [TTT02, p. 40]. Implicit C-state frames are introduced by TTP/C to reduce the frame overhead.

FlexRay and TTP/C provides the system state periodically by use of multiple nodes. A different approach is used by Time-Triggered Controller Area Network (TTCAN), which incorporates the concept of multiple time masters [Füh+01]. However, during operation, only a single time master is active, responsible for providing its view of the system state by periodic reference message transmissions to all other nodes.

TTEthernet, as a switched network technology, encapsulates and distributes the system state inside IEEE 802.3 compliant Ethernet frames. The system state information is transmitted periodically inside Protocol Control Frames (PCFs). PCFs can be specified further to cover different purposes. The Integration Frame (IN) represents such a PCF specification used for node integration [Ste09]. They are created by Synchronization Masters (SMs) and transmitted to all Compression Masters (CMs) where they are processed. The resulting IN is finally transmitted back to all SMs. Compared to the bus-based technologies, it is not possible to use the received system state information without initial preprocessing by the CMs. The processed IN contains the actual system state and a membership field, which represents the number of already synchronized SMs. The integration can be completed successfully if a sufficient number of SMs are active.

# 2.8 Clock Synchronization

Uncertainties of physical oscillators lead to local clock drifts over time, which can't be entirely removed. Clock synchronization is used to align all local

clocks of a system within predefined boundaries. This alignment process is applied continuously throughout synchronous operation in order to keep the clock deviations shorter or equal to the allowed precision.

The problem of clock synchronization inside distributed systems was first addressed in [Lam78]. However, the introduced approach relies on a fault-free message exchange between all system nodes. As a consequence, a single faulty node can corrupt the whole system. Further research regarding fault-tolerant clock synchronization was published in [LM85]. Its results are the foundation for many other clock synchronization algorithms, including the fault-tolerant midpoint algorithm [LL88] used for this thesis.

Clock synchronization can be applied in different ways [KAH04]. One solution is *clock state correction* intending to correct clock values immediately to remove the deviation that was accumulated over time. However, this correction only removes the effect of oscillator drifts but doesn't prevent clocks from drifting apart again. The clock drifting itself can be reduced by applying *clock rate correction*. As explained in Section 2.2, clocks derive their values by counting oscillator events. This counting correlates to the rate of a clock. Rate correction adjusts the counting to decrease or increase the rate of a clock to compensate oscillator uncertainties.

It might be sufficient to use only rate correction for specific applications. This can be done if systems work on time differences instead with time values, as explained in [Lis91]. However, widely used time-triggered technologies like FlexRay, TTP/C, or TTEthernet combine both correction methods to achieve better synchronization and to tolerate less precise oscillators.

Clock synchronization can be further distinguished in internal and external synchronization. For internal synchronization, an ensemble of clocks is defined and used to synchronize their clocks. External synchronization is used if an ensemble of clocks is defined but synchronized to a separated single or an ensemble of clocks.

#### 2.8.1 Processing Order

The process of clock synchronization can be defined generally in three steps. Initially, a node inside a system collects clock time values of other predefined nodes. These values are also called remote clock estimates and represent a relation between local clocks. The remote clock estimation was distinguished in two major approaches by [AP98, p. 13]. For time transmission techniques, a local clock value is sent by node  $N_i$ , based on its local time, to node  $N_n$ . The reception point in time at node  $N_n$  allows the estimation. However, latencies of the local clock distribution must be considered because it can affect the remote clock estimation quality drastically. The Remote Clock Reading (RCR) technique describes a request based remote clock estimation. Node  $N_i$  can trigger a local clock transmission at node  $N_n$  if required. The remote clock estimation additionally contains the request transmission latency.

Nodes can gather single or multiple remote clock estimates depending on the system. All these estimates, or a subset of them, are used to calculate a correction value for its local clock. Multiple remote clock estimates allow a fault-tolerant correction value calculation by discarding the extremes. The computation is done by *convergence functions* which are outlined more detailed in Section 2.8.2.

Finally, nodes use the prior calculated correction values to correct its local clock. The point in time and the way of correction value application differs between clock rate and state corrections.

# 2.8.2 Convergence Functions

Convergence functions take a set of remote clock estimates as inputs and provide a correction value used to correct a local clock. A detailed introduction of convergence functions is provided by [Sch86]. The work also contains evaluations of precision and accuracy boundaries for each investigated convergence function. An extended evaluation and classification of convergence functions is provided in [AP98, p. 19]. It defines *convergence-average* and *nonconvergence-average* techniques. For convergence-average techniques, a concrete clock value inside remote clock estimates is required to define

the correction value. Nonconvergence-average techniques only work with the presence of remote clock estimates. Convergence functions generally differ in computation complexity and their ability to tolerate faulty remote clock estimates.

Two convergence functions which are integrated in widely used communication technologies are given in the following. Notation  $f(p_i, x_i, ...x_n)$  identifies a convergence function, where  $p_i$  is the processor or node that intends to execute the convergence function and  $x_i, ...x_n$  represents the received remote clock estimates of  $p_i$ .

Fault-tolerant midpoint function. This function  $f_{ftm}(p_i, x_1, ...x_n)$  is used by FlexRay [Fle10, p. 213] and has been introduced initially by [LL88]. The algorithm discards the k highest and lowest remote clock estimates. From the remaining values,  $x_{high}$  and  $x_{low}$  are used to calculate a midpoint that serves as the correction value. Parameter k depends on n, but the maximum number of discarded values is bounded to four (two lowest, two highest). The algorithm complexity can be considered moderate because it requires only the sorting of values and a division by two.

Fault-tolerant average function. This function  $f_{fta}(p_i, x_1, ...x_n)$  is utilized by TTP/C [TTT02, p. 56] and has been published in [Dol+83]. The algorithm has been further analyzed for usage in a loosely coupled distributed real-time system in [KO87].  $f_{fta}$  discards a prior defined number k of n received remote clock estimates. The remaining n-2k values are all used to calculate its average which is the final correction value. The algorithm complexity is similar to function  $f_{ftm}$ .

# 2.8.3 Technology Specific Application

The synchronization approach depends on multiple factors like network topology or required reliability. Bus-based network technologies like TTP/C and FlexRay often takes advantage of small message latencies and low jitters. Both technologies are designed to provide a fault-tolerant clock synchroniza-

tion. The general concept of collecting remote clock estimates is the same for FlexRay [Fle10, p. 209] [Rau07, p.53] and TTP/C [Kop03; KB03], although these technologies differ regarding its number of different synchronization frames. Several nodes transmit synchronization messages periodically, whereas all receiving nodes know the expected dispatch point in time due to the schedule. The comparison between actual and expected synchronization frame reception provides the remote clock estimates used for error correction. Multiple nodes are selected to provide these synchronization messages to allow fault tolerance depending on the underlying correction algorithm (convergence function).

Another bus topology is TTP/A that relies on a master based clock synchronization [KB03; KHE00]. A master periodically transmits specific fireworks frames that contains relevant information to establish a global time inside each reception node. Clock state correction is applied immediately after the reception of the second byte of each fireworks frame. The temporal distance or interval between the first two bytes of each fireworks frame is known and additionally measured by all receiving nodes. The interval value is used to adjust the local clock rate based on the measured deviation to the expected interval.

A different approach for aligning local clocks is applied by SAFEbus. It uses three different kinds of synchronization messages. *Initial Resync* messages for start-ups, *Long Resync* messages for integration and *Short Resync* messages to correct oscillator drifts [HD92]. These messages contain relevant information of the overall system state required to synchronize or integrate. However, all nodes finally synchronize on sync pulses, which is a low value on the communication bus, applied by all nodes at fixed points in time. The low value is recognized by all nodes and causes a freeze of local clocks. All local clocks continue running at the release of the sync pulse, which completes the synchronization process.

Message latencies in meshed networks can vary drastically, which causes significant jitters. However, the precise determination of latency and jitter is the foundation of synchronization for the bus-based technologies introduced in this Section. Hence, nodes connected by a meshed topology are not able to collect remote clock estimates within an acceptable uncertainty by just detecting the reception point in time of synchronization frames. Instead, other mechanisms need to be established that allow a determination of the synchronization message latency between transmitting and receiving nodes. Network Time Protocol (NTP) [Mil91] was defined to solve the problem for very large networks like the internet. It is suitable for applications with synchronization requirements of a few milliseconds. A better synchronization quality is often required for industrial automation, military systems, and many other domains. These applications can utilize the Precision Time Protocol (PTP), defined in standard IEEE 1588, to achieve a synchronization quality in the area of microseconds or even sub-microseconds [IS08, p. 2]. Although it is possible to realize PTP in software, hardware timestamping is required to get high accuracy clock synchronization [LEG12].

TTEthernet deploys the PTP of standard IEEE 1588 to apply a delay accumulation inside synchronization frames [AK07]. A synchronization frame can pass multiple switches until the destination nodes are reached. Each traversed switch adds its delay, which enables the receiving node to determine the expected dispatch time of the respective synchronization frame [Ste+06]. The synchronization process itself requires two distinct applications of convergence functions [TTT11, p. 22]. Initially, a set of nodes, defined as SM, send a synchronization frame to all connected nodes marked as CM. CMs, which generally provides switching functionality, collect all synchronization frames to apply a first convergence function. The result, a compressed synchronization frame, is sent back to all connected SMs where a second convergence function is executed. Depending on the number of CMs, each SM finally receives n compressed synchronization frames used for the clock correction. The maximum limit of compressed synchronization frames is set to three for each synchronization attempt [Obe11, p. 200].

# Chapter 3

# Field Programmable Gate Arrays

#### 3.1 Introduction

FPGAs are electronic devices capable of implementing user-defined hardware designs combined with a high degree of flexibility. The resources inside FPGAs are connected by control of configuration memories to provide required user functionalities. These memories are reconfigurable for the majority of available FPGAs, which allows rapid prototyping, inexpensive bug fixing, or functional updates. However, the fixed layout of FPGAs, e.g. hardware primitives, clk trees, and interconnect possibilities, are placed throughout manufacturing, which introduces disadvantages compared to ASICs. These disadvantages comprise an increase in silicon area and power consumption. A decreased performance must also be expected. Additionally, FPGA utilization is expensive if used for high quantity products. A detailed comparison about the area, performance and power gap between FPGAs and ASICs are given in [KR07]. The configuration of currently available FPGA devices is realized by three different memory types and introduced in the following.

Flash technology. These memories are based on the *floating gate* technology and utilized by Actel FPGAs [BSV11, p. 12]. An advantage of this

technology is the non-volatility. Additionally, radiation tests for a particular flash based FPGA have shown, that the configuration memory is not sensitive to Single Event Effects (SEEs) caused by radiation [Urb+13]. A drawback of this technology is the limited number of reconfiguration cycles [Mic15, Tab. 2-3].

SRAM technology. Utilized by most available FPGAs but requires a configuration each time the device is powered on because of its volatility. The configuration time is very short compared to flash-based devices. Additionally, this technology allows an infinite number of reconfiguration cycles [BSV11, p. 14]. A significant disadvantage of this technology is the sensitivity to ionizing radiation [Man+08; Caf+02].

Antifuse technology. The configuration of this memory type can only be applied once without any possibility of reconfiguration. High voltage is used to melt a resistance which permanently stores the required value inside each memory cell [BSV11, p. 13]. This type of configuration memory provides the maximum resistance against radiation effects.

FPGA designs are mainly written by use of Hardware Description Languages (HDLs) like VHDL [Soc08] or Verilog [IEE06] to provide a Register-Transfer Level (RTL) representation of the required functionality. Additionally, major Electronic Design Automation (EDA) vendors have started to support SystemVerilog [SG17] as a design language. Efforts in increasing the abstraction of hardware design development is ongoing by use of High-Level Synthesis (HLS). HLS enables FPGA designers to describe hardware in programming languages like C, C++, or SystemC, depending on the utilized compiler [Nan+16]. Evaluations between HLS and traditional HDL designing have shown that performance gains and reductions of development times are possible [Wan+15; PR09].

The remainder of this chapter is structured as follows. Section 3.2 provides an overview of the general FPGA architecture. The impact of radiation effects on electronic devices and its implications to FPGAs are discussed in

Section 3.3. The overall design flow is introduced in Section 3.4 followed by an overview of formal verification approaches given in Section 3.5. Aspects regarding traditionally applied functional simulation are covered in Section 3.6. Assertion-based verification is introduced in Section 3.7 due to its importance for simulation and formal verification. Finally, an overview of the most adopted verification framework is given in Section 3.8.

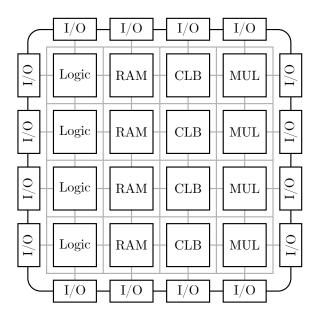

### 3.2 General Architecture

An abstract architecture of modern FPGAs is given in Figure 3.1 [KTR08]. It basically consists of functional blocks with the possibility of being intercon-

Figure 3.1: Basic FPGA architecture.

nected by routing channels. The configuration memory defines how the routing channels are configured and which blocks are actually connected to each other. A more detailed view on interconnect capabilities of meshed-based FPGA architectures is discussed in [PMM15, p. 48]. The given functional blocks can be classified into three types: I/O ports are used to connect the FPGA logic with external signals. Basic logic primitives provide the core

logic gates that are utilized for designs. Other blocks like Random-Access Memorys (RAMs), Multipliers (MULs), or hardware, used for creating and maintaining clks, can be treated as specialized ones.

A logic primitive can be configured to represent small boolean functions by utilizing Look-Up Tables (LUTs). Due to the interconnection capabilities, multiple logic primitives can be combined to implement arbitrary algorithms. Additionally, each logic primitive generally provides Flip-Flops (FFs), multiplexer, and special arithmetic functionality. Arithmetic functionalities are often provided by Digital Signal Processor (DSP) units as well.

It is recommended to use dedicated RAM units to store large data amounts instead of using FF. Otherwise, it is possible to run out of hardware resources that are required to implement the algorithms.

### 3.3 Radiation Effects

Electronic devices may be exposed to different types of radiation, which can be classified into two major categories: Charged particles (e.g. electrons) and electromagnetic radiation (e.g. ultraviolet light) [KCR06, p. 9]. The amount of energy which is deposited into a device is called Linear Energy Transfer (LET). It is defined by the deposited energy per unit path length (MeV/cm) divided by the density of the material  $(mg/cm^3)$  [BSV11, p. 44]. Electronic devices can be affected by radiation in different ways, ranging from transient to destructive effects. Devices can be shielded to reduce the overall dose level. However, shielding doesn't protect against SEEs caused by high energy particles [Duz05]. An overview of common radiation effects is given inside the following Sections 3.3.1 and 3.3.2.

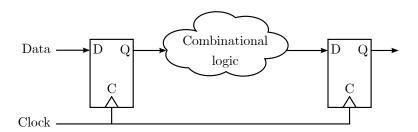

# 3.3.1 Single Event Effects

Different types of SEEs exist and generally classified by *soft errors* and *hard* errors [BSV11, p. 45].<sup>1</sup> An overview of common SEEs are introduced in the following with respect to typical circuit elements [KCR06, p. 13] given

<sup>&</sup>lt;sup>1</sup>SET, SEU and SEFI are soft errors. SEL is a hard error.

in Figure 3.2. These circuits generally consist of FFs and combinational

**Figure 3.2:** Typical circuit elements (combinational logic and flip-flops).

logic. FFs are used to define state machines or to store input values for further processing. Signals that are applied to combinational logic directly propagate through it. Additionally, combinational logic doesn't store any values. A circuit that defines its outputs based on its inputs and the actual memory content (state) is called sequential logic.

Single Event Transient (SET). SETs can occur in combinational logic of circuits. Charged particles that hit combinational logic can cause transient current spikes. The current spike can propagate to the output of the combinational logic, depending on its intensity. This, in turn, provides a probability of corrupting the system state, which happens in case current spikes and relevant clk edge events are present at FFs at the same time. The probability of corrupting FFs increases with higher system operating speeds [Dod+10].

Single Event Upset (SEU). SEUs can cause corruptions of memory elements [BSV11, p. 44]. It can happen to FFs, RAM cells used inside the circuit, but also to the configuration memory if SRAM based FPGAs are used. These effects are usually removed if the correct value is rewritten to the affected memory element. SEUs not necessarily implies an incorrect system behavior.

Single Event Functional Interrupt (SEFI). A SEFI is present if the radiation effect leads to a system that is not capable to continue a fault-free

operation [Kog+97]. This can happen if memory elements of state machines are corrupted or a program counter of processors.

Single Event Latch-up (SEL). SELs can cause permanent errors that induce a high current in the affected device [EDN04]. These high currents can be destructive if not recovered early enough by powering-off the device.

#### 3.3.2 Total Ionizing Dose

Total Ionizing Dose (TID) describes a cumulative radiation effect depending on exposure time, particle flux and its LET [BSV11, p. 49]. TID radiation hardness of Commercial Off-The-Shelf (COTS) microelectronic devices has been extended over the past decade [Dod+10]. However, it is still an important aspect to consider because of its degrading effects inside electronic devices. These degradation effects are various, depending on the electronic parts and the accumulated TID. For example, Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) threshold voltages can change which leads to increased currents or even result in complete losses of functionality [Mau+08]. During flash device tests, an increased single bit upset sensitivity was observed for relative low TID levels [Bag+10]. The correlation of TID to SEEs has be investigated in [Sal+16]. However, no correlation was observed for the tested parts.

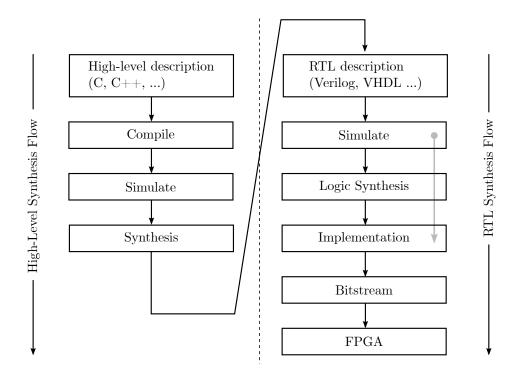

# 3.4 Design Flow

There are several approaches with different abstraction levels in use to implement hardware designs. A simplified design flow for recent Xilinx FPGA devices is shown in Figure 3.3. It can be divided into an optional HLS flow on the left side and the traditional RTL synthesis flow on the right side.

HLS is not a new approach. It started in the 1980s but failed to be adopted until the early 2000s. HLS tools generally focus on specific applications to achieve better results. Thus, it should not be utilized by default for all design types [MS09]. Xilinx HLS tool can process abstract hardware descriptions

Figure 3.3: High-level and register-transfer level synthesis flow.